# AIP3D15A060Q4T AIP3P15A060Q4T

# **Dual-In-Line Package Intelligent Power Module**

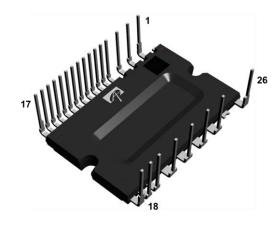

### **External View**

Size: 38 x 24 x 3.6 mm

### **Features**

- 3-phase inverter module with optional built-in PFC diode

- 600V-15A (Trench Shielded Planar Gate IGBT)

- Low V<sub>F</sub> and Ultra-fast recovery diode for PFC (AIP3P15A060Q4T)

- · Built-in bootstrap diodes with integrated current-limiting resistor

- Control supply under-voltage lockout protection (UVLO)

- Controllable over-temperature protection (OT)

- Temperature monitoring (V<sub>OT</sub>)

- Short-circuit current protection (C<sub>SC</sub>)

- Controllable fault out signal (V<sub>CF</sub>) corresponding to SC, UV and OT fault

- · Enable input functionality: Low-side IGBTs shut-down

- Input interface: 3 and 5V line, Schmitt trigger receiver circuit (Active high)

- Isolation ratings of 2000Vrms/min

## **Applications**

- AC 100-240Vrms class low power motor drives

- Air-conditioners, Washing machines, Compressors and Fan Motors

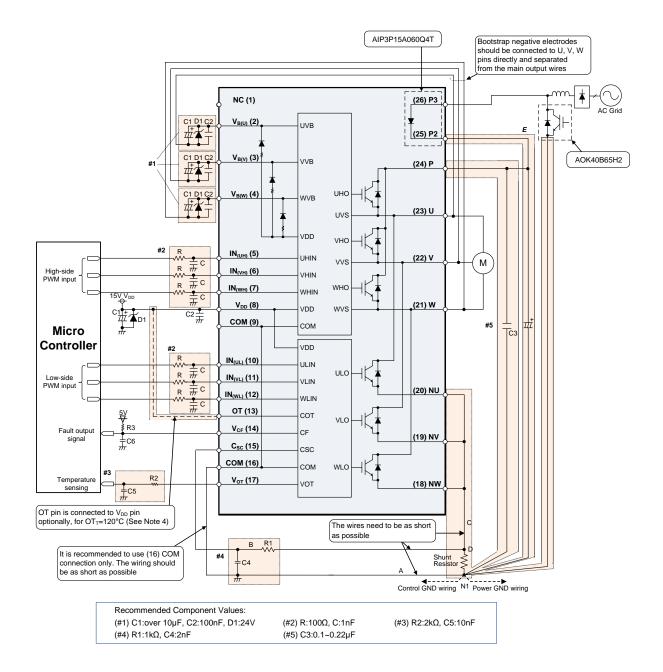

# Internal Equivalent Circuit / Pin Configuration

## **Ordering Information**

| Part Number    | Temperature Range | Package | Terminal type     |

|----------------|-------------------|---------|-------------------|

| AIP3D15A060Q4T | -40°C to 150°C    | IPM-3E  | Long with stopper |

| AIP3P15A060Q4T | -40°C to 150°C    | IPM-3F  | Long with stopper |

AOS Green Products use reduced levels of Halogens, and are also RoHS compliant. Please visit www.aosmd.com/media/AOSGreenPolicy.pdf for additional information.

# **Pin Description**

| Pin Number | Pin Name           | Pin Function                                                                            |

|------------|--------------------|-----------------------------------------------------------------------------------------|

| 1          | NC                 | No Connection                                                                           |

| 2          | $V_{B(U)}$         | High-Side Bias Voltage for U-Phase IGBT Driving                                         |

| 3          | $V_{B(V)}$         | High-Side Bias Voltage for V-Phase IGBT Driving                                         |

| 4          | $V_{B(W)}$         | High-Side Bias Voltage for W-Phase IGBT Driving                                         |

| 5          | IN <sub>(UH)</sub> | Signal Input for High-Side U-Phase                                                      |

| 6          | IN <sub>(VH)</sub> | Signal Input for High-Side V-Phase                                                      |

| 7          | IN <sub>(WH)</sub> | Signal Input for High-Side W-Phase                                                      |

| 8          | $V_{DD}$           | Common Bias Voltage for IC and IGBTs Driving                                            |

| 9          | COM                | Common Supply Ground                                                                    |

| 10         | IN <sub>(UL)</sub> | Signal Input for Low-Side U-Phase                                                       |

| 11         | IN <sub>(VL)</sub> | Signal Input for Low-Side V-Phase                                                       |

| 12         | IN <sub>(WL)</sub> | Signal Input for Low-Side W-Phase                                                       |

| 13         | OT                 | Controllable Over Temperature Protection (Connected to V <sub>DD</sub> for 120°C setup) |

| 14         | $V_{CF}$           | Controllable Fault Output                                                               |

| 15         | $C_{SC}$           | Capacitor (Low-Pass Filter) for Short-circuit Current Detection Input                   |

| 16         | COM                | Common Supply Ground                                                                    |

| 17         | V <sub>OT</sub>    | Voltage Output of LVIC Temperature                                                      |

| 18         | NW                 | Negative DC-Link Input for W-Phase                                                      |

| 19         | NV                 | Negative DC-Link Input for V-Phase                                                      |

| 20         | NU                 | Negative DC-Link Input for U-Phase                                                      |

| 21         | W                  | Output for W-Phase                                                                      |

| 22         | V                  | Output for V-Phase                                                                      |

| 23         | U                  | Output for U-Phase                                                                      |

| 24         | Р                  | Positive DC-Link Input                                                                  |

| 25         | P2                 | PFC Diode Cathode (AIP3P15A060Q4T)                                                      |

| 26         | P3                 | PFC Diode Anode (AIP3P15A060Q4T)                                                        |

Rev.1.0 September 2020 www.aosmd.com Page 2 of 15

## **Absolute Maximum Ratings**

$T_J = 25$ °C, unless otherwise specified.

| Symbol                 | Parameter                                                                  | Conditions                                                                                                                                        | Ratings              | Units            |

|------------------------|----------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------|----------------------|------------------|

| Inverter               |                                                                            |                                                                                                                                                   |                      |                  |

| $V_{PN}$               | Supply Voltage                                                             | Applied between P - NU,NV,NW                                                                                                                      | 450                  | V                |

| V <sub>PN(surge)</sub> | Supply Voltage (surge)                                                     | Applied between P - NU,NV,NW                                                                                                                      | 500                  | V                |

| V <sub>CES</sub>       | Collector-Emitter Voltage                                                  |                                                                                                                                                   | 600                  | V                |

|                        | Output Dhase Comment                                                       | T <sub>C</sub> =25°C, T <sub>J</sub> <150°C                                                                                                       | 15                   | А                |

| I <sub>C</sub>         | Output Phase Current                                                       | T <sub>C</sub> =80°C, T <sub>J</sub> <150°C                                                                                                       | 10                   | А                |

| ±I <sub>PK</sub>       | Output Peak Phase Current                                                  | T <sub>C</sub> =25°C, less than 1ms pulse width                                                                                                   | 30                   | А                |

| t <sub>SC</sub>        | Short Circuit Withstand Time                                               | V <sub>PN</sub> ≤400V, T <sub>J</sub> =150°C, V <sub>DD</sub> =15V                                                                                | 5                    | μs               |

| Pc                     | Collector Dissipation                                                      | T <sub>C</sub> =25°C, per chip                                                                                                                    | 33                   | W                |

| $T_J$                  | Operating Junction Temperature                                             |                                                                                                                                                   | -40 to 150           | °C               |

| PFC Diode              |                                                                            |                                                                                                                                                   |                      |                  |

| $V_{RRM}$              | Repetitive peak Reverse Voltage                                            | Applied between P2 – P3                                                                                                                           | 650                  | V                |

|                        | Output Phase Current                                                       | T <sub>C</sub> =25°C, T <sub>J</sub> <150°C                                                                                                       | 30                   | А                |

| l <sub>F</sub>         |                                                                            | T <sub>C</sub> =100°C, T <sub>J</sub> <150°C                                                                                                      | 15                   | А                |

| Control (P             | rotection)                                                                 |                                                                                                                                                   |                      |                  |

| $V_{DD}$               | Control Supply Voltage                                                     | Applied between V <sub>DD</sub> -COM                                                                                                              | 25                   | V                |

| $V_{DB}$               | High-Side Control Bias Voltage                                             | Applied between V <sub>B(U)</sub> -U, V <sub>B(V)</sub> -V, V <sub>B(W)</sub> -W                                                                  | 25                   | V                |

| V <sub>IN</sub>        | Input Voltage                                                              | Applied between IN <sub>(UH)</sub> , IN <sub>(VH)</sub> , IN <sub>(WH)</sub> , IN <sub>(UL)</sub> , IN <sub>(VL)</sub> , IN <sub>(WL)</sub> – COM | V <sub>DD</sub> +0.3 | V                |

| V <sub>CF</sub>        | Fault Output Supply Voltage                                                | Applied between V <sub>CF</sub> -COM                                                                                                              | COM+5.5              | V                |

| I <sub>CF</sub>        | Fault Output Current                                                       | Sink current at V <sub>CF</sub> terminal                                                                                                          | 1                    | mA               |

| V <sub>SC</sub>        | Current Sensing Input Voltage                                              | Applied between C <sub>SC</sub> -COM                                                                                                              | COM+5.5              | V                |

| V <sub>OT</sub>        | Temperature Output                                                         | Applied between V <sub>OT</sub> -COM                                                                                                              | COM+5.5              | V                |

| Total Syst             | em                                                                         |                                                                                                                                                   |                      |                  |

| V <sub>PN(PROT)</sub>  | Self Protection Supply Voltage Limit (Short-Circuit Protection Capability) | V <sub>DD</sub> =13.5-16.5V, Inverter part<br>T <sub>J</sub> =150°C, Non-repetitive, less than 2μs                                                | 400                  | V                |

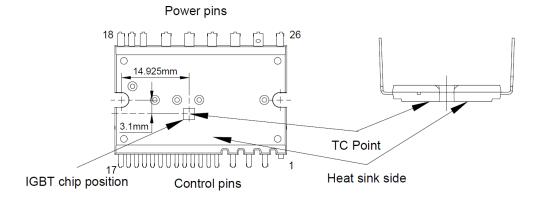

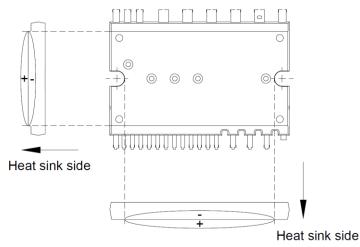

| T <sub>C</sub>         | Module Case Operation Temperature                                          | Measurement point of T <sub>C</sub> is provided in Figure 1                                                                                       | -30 to 125           | °C               |

| T <sub>STG</sub>       | Storage Temperature                                                        |                                                                                                                                                   | -40 to 150           | °C               |

| V <sub>ISO</sub>       | Isolation Voltage                                                          | 60Hz, sinusoidal, AC 1min, between connected all pins and heat sink plate                                                                         | 2000                 | V <sub>rms</sub> |

Figure 1. T<sub>C</sub> Measurement Point

Rev.1.0 September 2020 www.aosmd.com Page 3 of 15

## **Thermal Resistance**

| Symbol                | Parameter                               | Conditions                     | Min. | Тур. | Max. | Units |

|-----------------------|-----------------------------------------|--------------------------------|------|------|------|-------|

| R <sub>th(j-c)Q</sub> | Junction to Case Thermal Resistance (1) | Inverter IGBT (per 1/6 module) | ı    | ı    | 3.8  | K/W   |

| R <sub>th(j-c)F</sub> |                                         | Inverter FWD (per 1/6 module)  | ı    | ı    | 4.97 | K/W   |

| $R_{th(j-c)D}$        |                                         | PFC Diode (AIP3P15A060Q4T)     | -    | -    | 2.58 | K/W   |

### Note:

## **Electrical Characteristics**

$T_J = 25$ °C, unless otherwise specified.

| Symbol               | Parameter                                   | Conditions                                                        |                                                                                              | Min.  | Тур. | Max.  | Units |  |  |

|----------------------|---------------------------------------------|-------------------------------------------------------------------|----------------------------------------------------------------------------------------------|-------|------|-------|-------|--|--|

| Inverter             | Inverter                                    |                                                                   |                                                                                              |       |      |       |       |  |  |

| \/                   | Collector-Emitter Saturation                | V <sub>DD</sub> =V <sub>DB</sub> =15V,                            | I <sub>C</sub> =7.5A, T <sub>J=</sub> 25°C                                                   | -     | 1.40 | 1.90  | V     |  |  |

| $V_{CE(SAT)}$        | Voltage                                     | V <sub>IN</sub> =5V                                               | I <sub>C=7.5</sub> A, T <sub>J</sub> =125°C                                                  | -     | 1.60 | -     | V     |  |  |

| $V_{F}$              | FWD Forward Voltage                         | V <sub>IN</sub> =0                                                | I <sub>F</sub> =7.5A, T <sub>J</sub> =25°C                                                   | -     | 1.55 | 2.00  | V     |  |  |

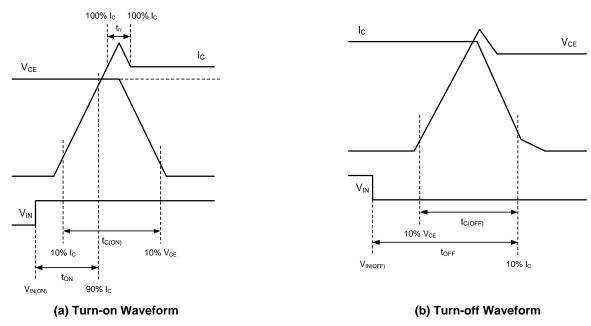

| ton                  |                                             |                                                                   |                                                                                              | 0.40  | 0.70 | 1.20  | μs    |  |  |

| $t_{C(ON)}$          |                                             | $V_{PN}$ =300V, $V_{DD}$ = $V_{DB}$                               | =15V                                                                                         | -     | 0.15 | 0.40  | μs    |  |  |

| $t_{OFF}$            | Switching Times                             | I <sub>C</sub> =10A, T <sub>J</sub> =25°C, V <sub>I</sub>         | $N=0V \leftrightarrow 5V$                                                                    | -     | 1.25 | 1.75  | μs    |  |  |

| $t_{C(OFF)}$         |                                             | Inductive load                                                    |                                                                                              | -     | 0.10 | 0.30  | μs    |  |  |

| t <sub>rr</sub>      |                                             |                                                                   |                                                                                              | -     | 0.10 | -     | μs    |  |  |

| loso                 | Collector-Emitter Leakage                   | V <sub>CE</sub> =V <sub>CES</sub>                                 | T <sub>J</sub> =25°C                                                                         | -     | -    | 1     | mA    |  |  |

| I <sub>CES</sub>     | Current                                     | VCE=VCES                                                          | T <sub>J</sub> =125°C                                                                        | -     | -    | 10    | mA    |  |  |

| PFC Diode            |                                             |                                                                   |                                                                                              |       |      |       |       |  |  |

| $V_{F}$              | FWD Forward Voltage                         |                                                                   | I <sub>F</sub> =20A, T <sub>J</sub> =25°C                                                    | -     | 1.45 | -     | V     |  |  |

| T <sub>rr</sub>      | Reverse recovery time                       |                                                                   | ·                                                                                            |       |      |       | ns    |  |  |

| $Q_{rr}$             | Reverse recovery Charge                     | T <sub>1</sub> =25°C V <sub>D</sub> =400V                         |                                                                                              | 0.55  |      | uC    |       |  |  |

| Irr                  | Peak reverse recovery current               | 15-20 0, VK-100V,                                                 | T <sub>J</sub> =25°C, V <sub>R</sub> =400V, I <sub>F</sub> =20A, dI <sub>F</sub> /dt=300A/us |       |      |       | Α     |  |  |

| Control (P           | Protection)                                 |                                                                   |                                                                                              |       |      |       |       |  |  |

| $I_{QDD}$            | Quiescent V <sub>DD</sub> Supply<br>Current | V <sub>DD</sub> =15V,<br>IN <sub>(UH,VH,WH,UL,VL,WL)</sub><br>=0V | V <sub>DD</sub> -COM                                                                         | -     | -    | 2.1   | mA    |  |  |

| I <sub>QDB</sub>     | Quiescent V <sub>DB</sub> Supply<br>Current | V <sub>DB</sub> =15V,<br>IN <sub>(UH, VH, WH)</sub> =0V           | $V_{B(U)}\text{-}U,V_{B(V)}\text{-}V,V_{B(W)}\text{-}W$                                      | -     | -    | 0.3   | mA    |  |  |

| $V_{\text{SC(ref)}}$ | Short-Circuit Trip Level                    | V <sub>DD</sub> =15V (2)                                          |                                                                                              | 0.455 | 0.48 | 0.505 | V     |  |  |

| $UV_{DT}$            |                                             | Trip Level                                                        |                                                                                              | 10.3  | 11.4 | 12.5  | V     |  |  |

| $UV_DR$              | Supply Circuit Under-Voltage                | Reset Level                                                       |                                                                                              | 10.8  | 11.9 | 13.0  | V     |  |  |

| $UV_DBT$             | Protection                                  | Trip Level                                                        |                                                                                              | 8.5   | 9.5  | 10.5  | V     |  |  |

| $UV_DBR$             |                                             | Reset Level                                                       |                                                                                              | 9.5   | 10.5 | 11.5  | V     |  |  |

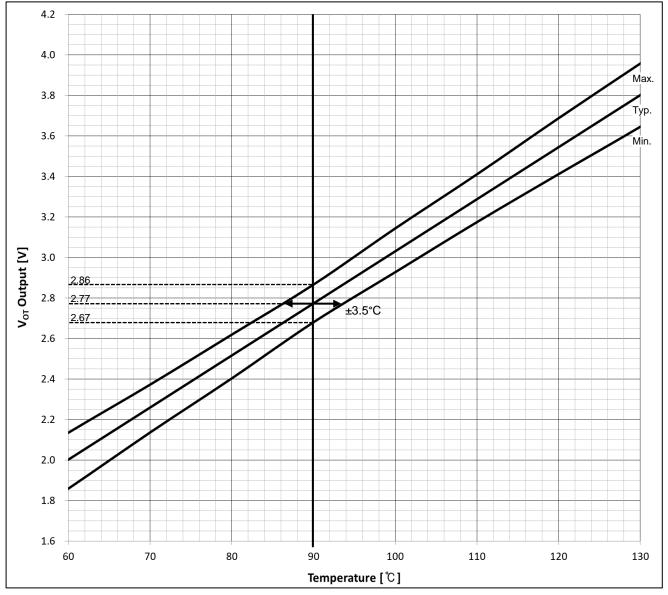

|                      | Temperature Output (3)                      |                                                                   | LVIC Temperature=90°C                                                                        | 2.67  | 2.77 | 2.86  | V     |  |  |

| V <sub>OT</sub>      | remperature Output                          |                                                                   | LVIC Temperature=25°C                                                                        | 0.8   | 1.05 | 1.3   | V     |  |  |

| OT <sub>T</sub>      | Over-Temperature                            | The OT Pin is                                                     | Trip Level                                                                                   | 100   | 120  | 140   | °C    |  |  |

| OT <sub>HYS</sub>    | Protection (4)                              | connected to V <sub>DD</sub> or open                              | Hysteresis of Trip Reset                                                                     | -     | 30   | -     | °C    |  |  |

Rev.1.0 September 2020 www.aosmd.com Page 4 of 15

<sup>1.</sup> For the measurement point of case temperature  $(T_{\mathbb{C}})$ , please refer to Figure 1.

| Symbol               | Parameter                              | Conditions                                                                                                         | Min. | Тур. | Max. | Units |  |  |

|----------------------|----------------------------------------|--------------------------------------------------------------------------------------------------------------------|------|------|------|-------|--|--|

| Control (P           | Control (Protection)                   |                                                                                                                    |      |      |      |       |  |  |

| $V_{CFH}$            | Foult Output Valtage                   | V <sub>SC</sub> =0V, V <sub>CF</sub> Circuit: 10kΩ to 5V pull-up                                                   | 4.9  | -    | -    | V     |  |  |

| $V_{CFL}$            | Fault Output Voltage                   | V <sub>SC</sub> =1V, V <sub>CF</sub> Circuit: 10kΩ to 5V pull-up                                                   | -    | -    | 0.5  | V     |  |  |

| V <sub>CF+</sub>     | CF positive going threshold            |                                                                                                                    | -    | 1.9  | 2.2  | V     |  |  |

| V <sub>CF</sub> -    | CF negative going threshold            |                                                                                                                    | 0.8  | 1.1  | -    | V     |  |  |

|                      |                                        | Pull-up resistor only                                                                                              | 20   | -    | -    | μs    |  |  |

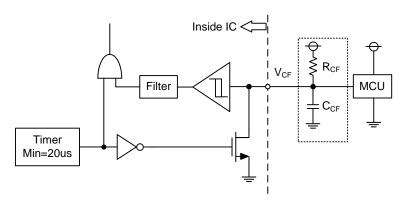

| t <sub>FO</sub>      | Fault Output Pulse Width (5)           | Pull-up resistor with pull-down capacitor ( $R_{CF}$ =2.2 $M\Omega$ , $C_{CF}$ =1 $nF$ , 5 $V$ pull-up) (Figure 5) | -    | 1    | -    | ms    |  |  |

| I <sub>IN</sub>      | Input Current                          | V <sub>IN</sub> =5V                                                                                                | -    | 0.72 | -    | mA    |  |  |

| V <sub>th(on)</sub>  | ON Threshold Voltage                   |                                                                                                                    |      | 2.3  | 2.6  | V     |  |  |

| V <sub>th(off)</sub> | OFF Threshold Voltage                  | Applied between IN <sub>(UH)</sub> , IN <sub>(VH)</sub> , IN <sub>(WH)</sub> , IN <sub>(UL)</sub> ,                | 0.8  | 1.2  |      | V     |  |  |

| V <sub>th(hys)</sub> | ON/OFF Threshold<br>Hysteresis Voltage | IN <sub>(VL)</sub> , IN <sub>(WL)</sub> -COM                                                                       | -    | 1.1  | -    | V     |  |  |

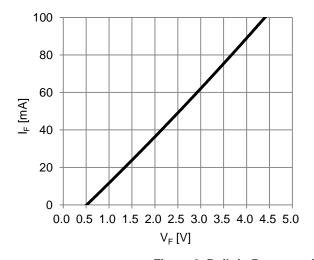

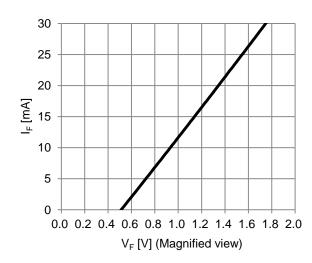

| V <sub>F(BSD)</sub>  | Bootstrap Diode Forward<br>Voltage     | I <sub>F</sub> =10mA Including Voltage Drop by Limiting Resistor <sup>(6)</sup>                                    | 0.5  | 1.0  | 1.5  | V     |  |  |

| R <sub>BSD</sub>     | Built-in Limiting Resistance           | Included in Bootstrap Diode                                                                                        | 80   | 100  | 120  | Ω     |  |  |

### Notes:

- 2. Short-circuit protection works only for low sides.

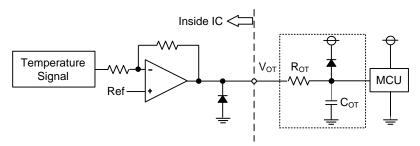

- When temperature exceeds the protective level that the user defined, the controller (MCU) should stop the IPM. Temperature of LVIC vs. V<sub>OT</sub> output characteristics is described in Figure 3.

- When the LVIC temperature exceeds OT Trip temperature level (OT<sub>T</sub>), OT protection is triggered and fault outputs. OT Trip level can be adjusted by pull-down resistors values as shown in the table below.

| OT Pin                  | OT <sub>⊤</sub> [°C] |

|-------------------------|----------------------|

| 10kΩ                    | Disable              |

| 100kΩ                   | 130                  |

| 400kΩ                   | 110                  |

| V <sub>DD</sub> or Open | 120                  |

- Fault signal (F<sub>O</sub>) outputs when SC, UV or OT protection is triggered. F<sub>O</sub> pulse width is different for each protection mode. At SC failure, F<sub>O</sub> pulse width is fixed (minimum 20µs) or controlled by RC network (see Figure 5), but at UV or OT failure, F<sub>O</sub> outputs continuously until recovering from UV or OT state.

- 6. The characteristics of bootstrap diodes are shown in Figure 2.

Figure 2. Built-in Bootstrap Diode V<sub>F</sub>-I<sub>F</sub> Characteristic (T<sub>C</sub>=25°C)

Rev.1.0 September 2020 www.aosmd.com Page 5 of 15

Figure 3. Temperature of LVIC vs. VoT Output Characteristics

- (1) In the case of using  $V_{OT}$  with low voltage controller like 3.3V MCU,  $V_{OT}$  output might exceed control supply voltage 3.3V when temperature rises excessively. If system uses low voltage controller, it is recommended to insert a clamp diode between control supply of the controller and  $V_{OT}$  output for preventing over voltage destruction.

- (2) When  $V_{OT}$  is connected to MCU, to use RC ( $R_{OT}$ =2 $k\Omega$ ,  $C_{OT}$ =10nF) filter is recommended.

- (3) In the case of not using  $V_{\text{OT}}$ , leave  $V_{\text{OT}}$  output NC (No connection).

Figure 4. Interface Circuit at Pin VoT

Rev.1.0 September 2020 www.aosmd.com Page 6 of 15

- (1) The V<sub>CF</sub> pin combines three functions in one pin: Fixed fault out, Controllable fault out pulse width based on RC network, and Enable input.

- (2) The V<sub>CF</sub> pin provides an enable functionality that allows it to shut down the all low-side IGBTs. When the V<sub>CF</sub> pin is in the high state the IPM is able to operate normally. If the V<sub>CF</sub> pin is in a low state, the low-side IGBTs are turned off until the enable condition is restored. In addition, the V<sub>CF</sub> pin can provide the fault output signal with the fixed or controlled fault outputse width.

- (3) If a pull-up resistor (10kΩ) only is connected to the V<sub>CF</sub> pin, the fault output pulse width is fixed at minimum 20us.

- (4) If a capacitor (C<sub>CF</sub>) is connected with a pull-up resistor (R<sub>CF</sub>) together, the fault output pulse width can be controlled according to the resistor and the capacitor values. The length of fault output pulse width is determined by the following formula:

- $t_{FO} = -(R_{CF} * C_{CF}) * ln(1 V_{CF} + / V_{DD}) + 100 ns + 20 us(min.)$

- ex)  $V_{DD}=5V$ ,  $R_{CF}=2.2M\Omega$ ,  $C_{CF}=1nF$ ,  $t_{FO}\approx1.07ms$ . Recommended parameters in the design are  $C_{CF}$  of  $\leq 1nF$  and  $R_{CF}$  of 0.1M to 2.2M $\Omega$ .

Figure 5. Interface Circuit at Pin V<sub>CF</sub>

Rev.1.0 September 2020 www.aosmd.com Page 7 of 15

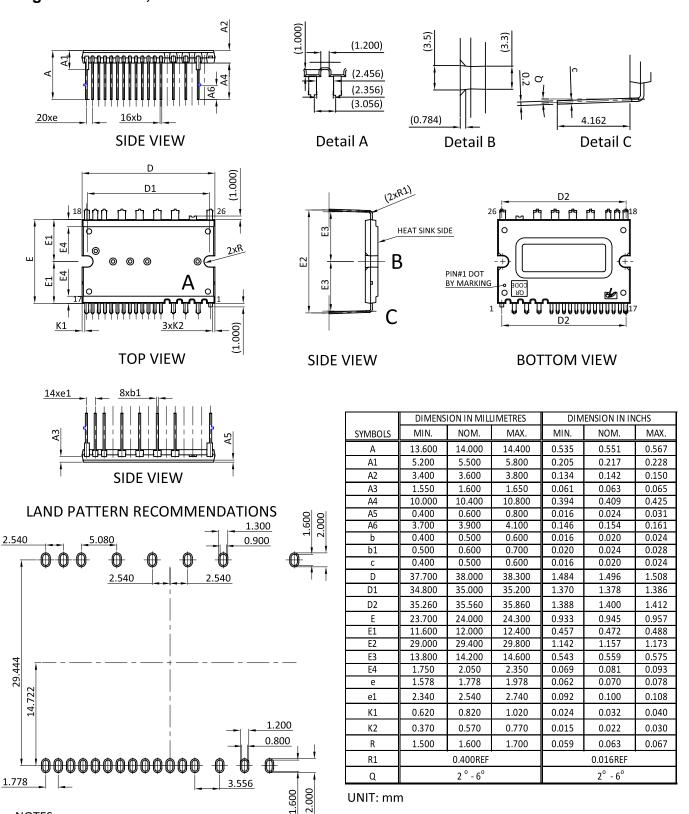

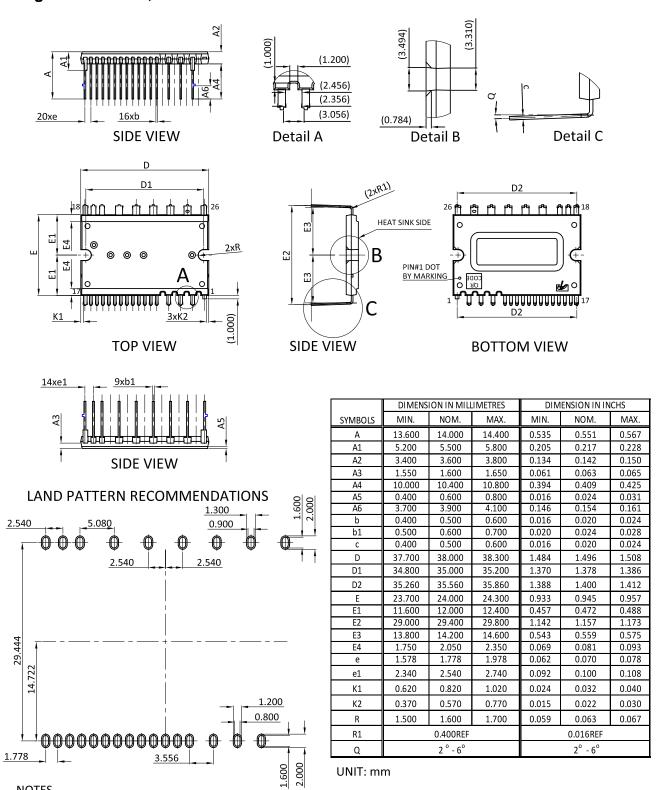

# **Mechanical Characteristics and Ratings**

| Symbol          | Parameter              | Conditions | Min. | Тур. | Max. | Units |

|-----------------|------------------------|------------|------|------|------|-------|

| Mounting Torque | Mounting Screw: M3 (7) |            | 0.59 | 0.69 | 0.78 | N m   |

| Weight          |                        |            | -    | 9.12 | -    | g     |

| Flatness        | Refer to Figure 6      |            | -50  | -    | 100  | μm    |

### Note:

7. Plain washers (ISO 7089-7094) are recommended.

**Figure 6. Flatness Measurement Position**

## **Recommended Operation Conditions**

| Symbol                      | Parameter                                 | Conditions                                                  | Min. | Тур. | Max. | Units |

|-----------------------------|-------------------------------------------|-------------------------------------------------------------|------|------|------|-------|

| V <sub>PN</sub>             | Supply Voltage                            | Applied between P-NU, NV, NW                                | 0    | 300  | 400  | V     |

| $V_{DD}$                    | Control Supply Voltage                    | Applied between V <sub>DD</sub> -COM                        | 13.5 | 15.0 | 16.5 | V     |

| $V_{DB}$                    | High-Side Bias Voltage                    | Applied between $V_{B(U)}$ -U, $V_{B(V)}$ -V, $V_{B(W)}$ -W | 13.5 | 15.0 | 18.5 | V     |

| $dV_{DD}/dt$ , $dV_{DB}/dt$ | Control Supply Variation                  |                                                             | -1   | -    | +1   | V/µs  |

| t <sub>dead</sub>           | Arm Shoot-Through Blocking Time           | For each input signal                                       | 1.0  | -    | -    | μs    |

| f <sub>PWM</sub>            | PWM Input Frequency                       | -40°C < T <sub>J</sub> < 150°C                              | -    | -    | 20   | kHz   |

| PW <sub>IN(ON)</sub>        | Adia income la mont Doube a NA/i dula (8) |                                                             | 0.5  | -    | -    | μs    |

| PW <sub>IN(OFF)</sub>       | Minimum Input Pulse Width (8)             |                                                             | 0.5  | -    | -    | μs    |

| СОМ                         | COM Variation                             | Between COM-NU, NV, NW (including surge)                    | -5.0 | -    | 5.0  | V     |

### Note:

8. IPM may not respond if the input pulse width is less than  $\text{PW}_{\text{IN}(\text{ON})}, \text{PW}_{\text{IN}(\text{OFF})}.$

Rev.1.0 September 2020 www.aosmd.com Page 8 of 15

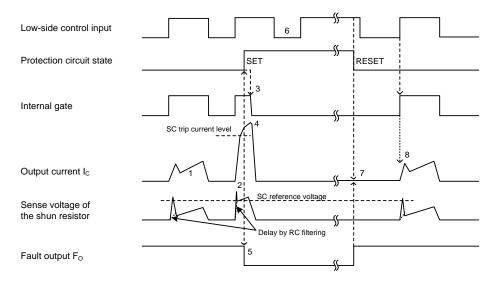

### Time Charts of the IPM Protective Function

- (1) Normal operation: IGBT turns on and outputs current.

- (2) Short-circuit current detection (SC triggered).

- (3) All low-side IGBTs' gates are hard interrupted.

- (4) All low-side IGBTs turn OFF.

- (5)  $F_O$  output time ( $t_{FO}$ )=minimum 20 $\mu$ s.

- (6) Input = "L": IGBT OFF.

- (7) Fault output finishes, but output current will not turn on until next ON signal ( $L\rightarrow H$ ).

- (8) Normal operation: IGBT turns on and outputs current.

Figure 7. Short-Circuit Protection (Low-side Operation Only with the External Shunt Resistor and RC Filter)

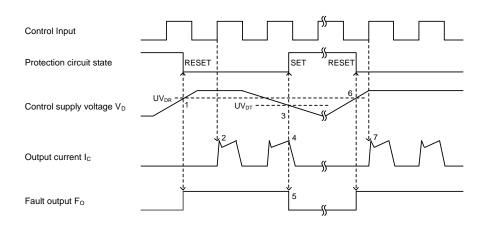

- (1) Control supply voltage  $V_{DD}$  exceeds under voltage reset level (UV<sub>DR</sub>), but IGBT turns on by next ON signal (L $\rightarrow$ H).

- (2) Normal operation: IGBT turns on and outputs current.

- (3) V<sub>DD</sub> level drops to under voltage trip level (UV<sub>DT</sub>).

- (4) All low-side IGBTs turn OFF regardless of control input condition.

- (5)  $F_O$  output time ( $t_{FO}$ )=minimum 20 $\mu$ s, and  $F_O$  stays low as long as  $V_{DD}$  is below  $UV_{DR}$ .

- (6) V<sub>DD</sub> level reaches UV<sub>DR</sub>.

- (7) Normal operation: IGBT turns on and outputs current.

Figure 8. Under-Voltage Protection (Low-side, UV<sub>D</sub>)

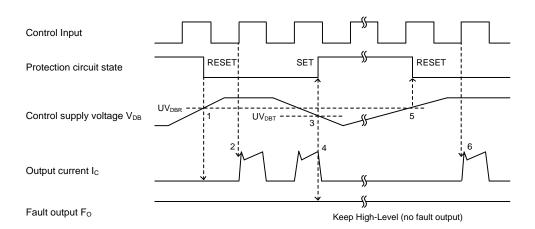

- (1) Control supply voltage  $V_{DB}$  rises. After the voltage reaches under voltage reset level  $UV_{DBR}$ , IGBT turns on by next ON signal (L $\rightarrow$ H).

- (2) Normal operation: IGBT turns on and outputs current.

- (3) V<sub>DB</sub> level drops to under voltage trip level (UV<sub>DBT</sub>).

- (4) All high-side IGBTs turn OFF regardless of control input condition, but there is no Fo signal output.

- (5) V<sub>DB</sub> level reaches UV<sub>DBR</sub>.

- (6) Normal operation: IGBT turns on and outputs current.

Figure 9. Under-Voltage Protection (High-side, UV<sub>DB</sub>)

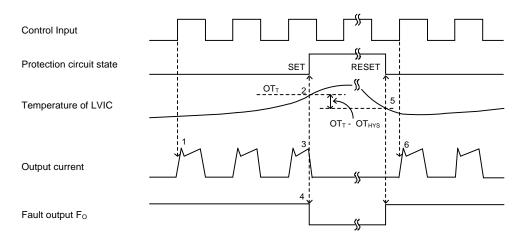

- (1) Normal operation: IGBT turns on and outputs current.

- (2) LVIC temperature exceeds over-temperature trip level (OT<sub>T</sub>).

- (3) All low-side IGBTs turn off regardless of control input condition.

- (4)  $F_O$  output time ( $t_{FO}$ )=minimum 20 $\mu$ s, and  $F_O$  stays low as long as LVIC temperature is over  $OT_T$ .

- (5) LVIC temperature drops to over-temperature reset level (OT<sub>T</sub>-OT<sub>HYS</sub>).

- (6) Normal operation: IGBT turns on by the next ON signal ( $L\rightarrow H$ ).

Figure 10. Over-Temperature Protection (Low-side, Detecting LVIC Temperature)

Rev.1.0 September 2020 www.aosmd.com Page 10 of 15

## **Example of Application Circuit**

- (1) GND pattern: The star ground design is recommended. GND pattern should be separated at the one point of the shunt resistors.

- (2) COM pin: It is recommended to only use the (16) COM pin to minimize SC detection noise. Leave pin (9) NC (No Connection).

- (3) A Zener diode D1 (24V/1W) is recommended between each pair of control supply pins to prevent surge destruction.

- (4) Snubber capacitor: The wiring between the IPM and snubber capacitor (C3) including the shunt resistors should be as short as possible.

- (5) C<sub>SC</sub> pin circuit: C4 should be placed as close to C<sub>SC</sub> pin and COM (16) pin as possible to prevent protection function errors.

- (6) P2 pin connection: The pin P2 (PFC diode cathode) should connected directly to the positive terminal of DC-link capacitor as shown in the trace E.

- (7) Bootstrap capacitors: It is recommended that all capacitors are mounted as close to the IPM as possible.

- (8) Input circuit: The R and C filter circuit should be mounted to reduce input signal noise by high speed switching. C should be placed as close to COM (16) pin as possible.

- (9) V<sub>CF</sub> pin circuit: V<sub>CF</sub> output is open drain type. The signal line should be pulled up to the positive side of the 5V/3.3V logic power supply with a proper resistor R3. For the detailed design guide, please refer to the Figure 5.

Rev.1.0 September 2020 www.aosmd.com Page 11 of 15

Figure 11. Switching Times Definition

Rev.1.0 September 2020 **www.aosmd.com** Page 12 of 15

## Package Dimensions, IPM3-3E

### **NOTES**

- 1. PACKAGE BODY SIZES EXCLUDE MOLD FLASH AND GATE BURRS, MOLD FLASH SHOULD BE LESS THAN 6 MIL.

- 2. TOLERANCE 0.100 MILLIMETERS UNLESS OTHERWISE SPECIFIED.

- 3. CONTROLLING DIMENSION IS MILLIMETER, CONVERTED INCH DIMENSIONS ARE NOT NECESSARILY EXACT.

4. () IS REFERENCE.

## Package Dimensions, IPM3-3F

- 1. PACKAGE BODY SIZES EXCLUDE MOLD FLASH AND GATE BURRS, MOLD FLASH SHOULD BE LESS THAN 6 MIL.

- 2. TOLERANCE 0.100 MILLIMETERS UNLESS OTHERWISE SPECIFIED.

- 3. CONTROLLING DIMENSION IS MILLIMETER, CONVERTED INCH DIMENSIONS ARE NOT NECESSARILY EXACT.

4. () IS REFERENCE.

٦

### **LEGAL DISCLAIMER**

Applications or uses as critical components in life support devices or systems are not authorized. AOS does not assume any liability arising out of such applications or uses of its products. AOS reserves the right to make changes to product specifications without notice. It is the responsibility of the customer to evaluate suitability of the product for their intended application. Customer shall comply with applicable legal requirements, including all applicable export control rules, regulations and limitations.

AOS' products are provided subject to AOS' terms and conditions of sale which are set forth at: <a href="http://www.aosmd.com/terms">http://www.aosmd.com/terms</a> and conditions of sale

### LIFE SUPPORT POLICY

ALPHA & OMEGA SEMICONDUCTOR PRODUCTS ARE NOT AUTHORIZED FOR USE AS CRITICAL COMPONENTS IN LIFE SUPPORT DEVICES OR SYSTEMS.

## As used herein:

- 1. Life support devices or systems are devices or systems which, (a) are intended for surgical implant into the body or (b) support or sustain life, and (c) whose failure to perform when properly used in accordance with instructions for use provided in the labeling, can be reasonably expected to result in a significant injury of the user.

- 2. A critical component in any component of a life support, device, or system whose failure to perform can be reasonably expected to cause the failure of the life support device or system, or to affect its safety or effectiveness.