# AOZ18101DI-03/04

4 V 20 mΩ Over-Voltage Protection Efuse

## **General Description**

AOZ18101DI-03/04 is a current-limiting over-voltage protection Efuse targeting applications that require front end protection at the input line. Both VIN and VOUT terminals are rated at 22 V absolute maximum. There is a programable soft-start feature that controls the inrush current for highly capacitive loads. It also has Input Under-Voltage Lock Out (UVLO), Input Over-Voltage Output Clamp (OVC), and Thermal Shut Down Protection (TSD).

AOZ18101DI-03/04 features an internal current-limiting circuit that protects the supply from large load current. The current limit threshold can be set externally with a resistor.

AOZ18101DI-03 is auto-restart version after fault condition. AOZ18101DI-04 is latch-off version after fault is detected. Both are available in small 3 mm x 3 mm 10-pin DFN package.

#### **Features**

- 3.5 V to 14 V input voltage operating range

- 22 V abs max voltage rating on VIN and VOUT pin

- Typical R<sub>ON</sub>: 20 mΩ

- 1A to 5A programmable current limit

- Programmable output soft start time

- Fast Over Current Protection (OCP)

- Input Over-Voltage Output Clamp (OVC)

- Input Under-Voltage Lock Out (UVLO)

- Thermal Shut Down Protection (TSD)

- ±2kV HBM ESD rating

- ±1 kV CDM ESD rating

- IEC 61000-4-2: ±8 kV on VIN and VOUT

- IEC 61000-4-5: ± 40 V on VIN, No cap

## **Applications**

- Servers

- HDD and SSD drivers

- PCI cards

- Networking

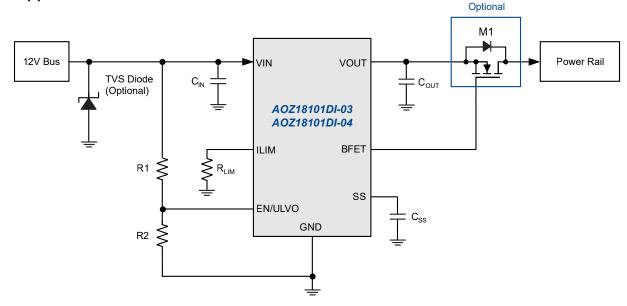

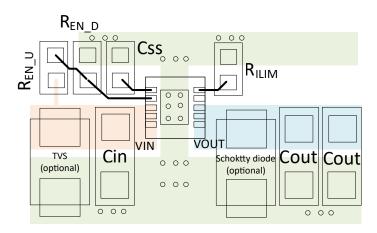

# **Typical Applications**

# **Ordering Information**

| Part Number   | Part Number Fault Recovery ( |              | Package    | Environmental |

|---------------|------------------------------|--------------|------------|---------------|

| AOZ18101DI-03 | Auto-Restart                 | 3.5 V – 14 V | DFN3x3-10L | RoHS          |

| AOZ18101DI-04 | Latch-Up                     | 3.5 V – 14 V | DFN3x3-10L | RoHS          |

AOS products are offered in packages with Pb-free plating and compliant to RoHS standards. Please visit <a href="https://www.aosmd.com/media/AOSGreenPolicy.pdf">www.aosmd.com/media/AOSGreenPolicy.pdf</a> for additional information.

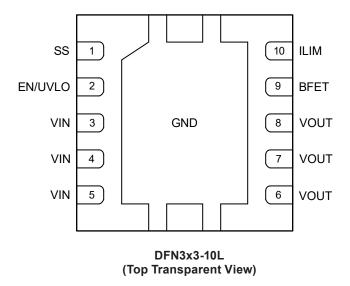

## **Pin Configuration**

# **Pin Description**

| Pin Number | Pin Name | Pin Function                                                                                                                                                                |  |  |

|------------|----------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| 1          | SS       | Soft-start control. Connect a capacitor C <sub>SS</sub> from SS to GND to set the soft-start time.                                                                          |  |  |

| 2          | EN/UVLO  | Enable input. Active high. It can be used as UVLO by connecting resistor divider from VIN.                                                                                  |  |  |

| 3, 4, 5    | VIN      | Supply input. Connected to main power supply. They are internally connected together.                                                                                       |  |  |

| 6, 7, 8    | VOUT     | Power output. They are internally connected together.                                                                                                                       |  |  |

| 9          | BFET     | External blocking FET gate control. This pin can be left open when it is not used. When external blocking FET is used, connect this pin to the gate of the blocking FET.    |  |  |

| 10         | ILIM     | Current limit set pin. Connect a 1% resistor RLIM from ILIM to GND to set the current limit threshold.                                                                      |  |  |

| EXP        | GND      | Ground. Connect to GND. For best thermal performance make the ground copper pads as large as possible and connect to EXP to the ground plane through multiple thermal VIAs. |  |  |

Rev. 1.0 December 2021 **www.aosmd.com** Page 2 of 13

# **Absolute Maximum Ratings**

Exceeding the Absolute Maximum ratings may damage the device.

| Parameter                              | Rating            |

|----------------------------------------|-------------------|

| VIN, VOUT to GND                       | -0.3 V to 22 V    |

| VOUT to GND Transient <1 µs            | -1.2V             |

| EN/UVLO, ILIM, SS to GND               | -0.3 V to 6 V     |

| BFET to GND                            | -0.3 V to 22 V    |

| Junction Temperature (T <sub>J</sub> ) | +150°C            |

| Storage Temperature (T <sub>S</sub> )  | -65 °C to +150 °C |

| ESD Rating HBM All Pins                | ±2kV              |

| IEC 61000-4-2: VOUT and VIN            | ±8kV              |

# **Recommended Operating Conditions**

The device is not guaranteed to operate beyond the Maximum Recommended Operating Conditions.

| Parameter                              | Rating          |

|----------------------------------------|-----------------|

| Supply Voltage VIN, VOUT to GND        | 3.5 V to 14 V   |

| BFET to GND                            | 0V to VOUT +6V  |

| EN/UVLO, ILIM, SS to GND               | 0 V to 5.5 V    |

| Switch DC Current (I <sub>SW</sub> )   | 0 A to 5A       |

| Junction Temperature (T <sub>J</sub> ) | -40°C to +125°C |

| Package Thermal Resistance             |                 |

| DFN3x3-10L (Θ <sub>JA</sub> )          | 65°C/W          |

#### Electrical Characteristics(1)

$\rm T_A$  = 25 °C, VIN = 12 V, EN = 5 V,  $\rm R_{LIM}$  = 100 k $\Omega$ , unless otherwise specified.

| Symbol                | Parameter                        | Conditions                                                                                | Min  | Тур  | Max  | Units |  |

|-----------------------|----------------------------------|-------------------------------------------------------------------------------------------|------|------|------|-------|--|

| General               |                                  |                                                                                           |      |      |      |       |  |

| V <sub>VIN</sub>      | Input Supply Voltage             |                                                                                           | 3.5  |      | 14   | V     |  |

| V <sub>UVLO_R</sub>   | Under-voltage Lockout Threshold  | VIN rising                                                                                | 2.9  |      | 3.4  | V     |  |

| V <sub>UVLO_HYS</sub> | Under-voltage Lockout Hysteresis | VIN falling                                                                               |      | 250  |      | mV    |  |

| I <sub>VIN_ON</sub>   | Input Quiescent Current          | IOUT = 0A                                                                                 |      | 500  |      | μA    |  |

| I <sub>VIN_OFF</sub>  | Input Shutdown Current           | EN/UVLO = 0 V                                                                             |      | 125  |      | μA    |  |

| V <sub>OVC</sub>      | Output Over-Voltage Clamp        | VIN = 17 V, I <sub>OUT</sub> = 10 mA                                                      | 14.0 | 15.0 | 16.5 | V     |  |

| Б                     | 0 11 01 5 11                     | VIN = 12V, I <sub>OUT</sub> = 1A                                                          |      | 20   |      |       |  |

| R <sub>ON</sub>       | Switch ON-Resistance             | VIN = 5 V, I <sub>OUT</sub> = 1 A                                                         |      | 21   |      | mΩ    |  |

| V <sub>EN_H</sub>     | EN Input Logic High Threshold    | EN/UVLO rising                                                                            | 1.3  | 1.40 | 1.45 | V     |  |

| V <sub>EN_L</sub>     | EN Input Logic Low Threshold     | EN/UVLO falling                                                                           | 1.2  | 1.35 | 1.4  | V     |  |

| I <sub>EN BIAS</sub>  | EN Input Pull-down Resistance    | EN/UVLO = 1.8 V                                                                           | -100 |      | 100  | nA    |  |

| Dynamic T             | Fiming Characteristics           |                                                                                           |      | •    |      |       |  |

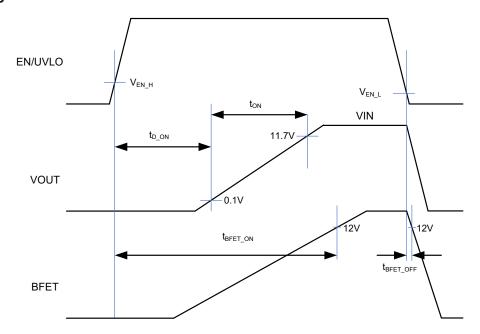

| t <sub>D_ON</sub>     | Turn-On Delay Time               | From EN/UVLO > $V_{EN\_H}$ to VOUT = 0.1 V. $C_{SS}$ = open                               | 420  | 600  | 780  | μs    |  |

| t <sub>on</sub>       | Turn-On Time                     | C <sub>SS</sub> = open                                                                    | 420  | 700  | 980  | μs    |  |

|                       | (VOUT from 0.1 V to 11.7 V)      | C <sub>SS</sub> = 1nF                                                                     |      | 12   |      | ms    |  |

| t <sub>D_OFF</sub>    | Turn-off Delay Time              | From EN/UVLO < V <sub>EN_L</sub> to BFET = falling down to 12V, C <sub>BFET</sub> = open  |      | 0.5  |      | μs    |  |

| t <sub>BFET_ON</sub>  | BFET Turn-On Time                | From EN/UVLO > V <sub>EN_H</sub> to BFET = rising above to 12V, C <sub>BFET</sub> = 1 nF  |      | 1.3  |      | ms    |  |

|                       | DELI TUTTI-ON TITTE              | From EN/UVLO > V <sub>EN_H</sub> to BFET = rising above to 12V, C <sub>BFET</sub> = 10 nF |      | 2.3  |      | ms    |  |

## Electrical Characteristics(1)

$\rm T_A$  = 25 °C, VIN = 12 V, EN = 5 V,  $\rm R_{LIM}$  = 100 k $\rm \Omega,$  unless otherwise specified.

| Symbol                         | Parameter                            | Conditions                                                                  | Min  | Тур  | Max  | Units |  |  |

|--------------------------------|--------------------------------------|-----------------------------------------------------------------------------|------|------|------|-------|--|--|

| Dynamic Timing Characteristics |                                      |                                                                             |      |      |      |       |  |  |

| t <sub>BFET_OFF</sub>          | BFET Turn-Off Time                   | From EN/UVLO < $V_{EN\_L}$ to BFET = falling down to 12V, $C_{BFET}$ = 1 nF |      | 6    |      | μs    |  |  |

|                                | BFET Turn-Oil Time                   | From EN/UVLO < $V_{EN_L}$ to BFET = falling down to 12V, $C_{BFET}$ = 10 nF |      | 50   |      | μs    |  |  |

| Over Curi                      | rent Protection (OCP)                |                                                                             |      |      |      |       |  |  |

|                                |                                      | R <sub>LIM</sub> = 150 kΩ                                                   | 4.50 | 5.10 | 5.70 | A     |  |  |

|                                |                                      | R <sub>LIM</sub> = 100 kΩ                                                   | 3.46 | 3.75 | 4.03 |       |  |  |

| I <sub>LIM</sub>               | Current Limt Threshold               | $R_{LIM} = 45.3 k\Omega$                                                    | 1.79 | 2.10 | 2.42 |       |  |  |

|                                |                                      | $R_{LIM} = 10 k\Omega$                                                      |      | 1.00 |      |       |  |  |

|                                |                                      | R <sub>LIM</sub> =0 or Open                                                 |      | 0.75 |      |       |  |  |

| I <sub>OCP_FAST</sub>          | Fast OCP Threshold for Current Spike | Based on I <sub>LIM</sub> value                                             |      | 160  |      | %     |  |  |

| t <sub>OCP_FAST</sub>          | Fast OCP Response Time               | From IOUT > (I <sub>LIM</sub> x 160%)                                       |      | 300  |      | ns    |  |  |

| Blocking FET Driver            |                                      |                                                                             |      |      |      |       |  |  |

| I <sub>BFET</sub>              | BFET Driving Current                 | BFET=VOUT                                                                   |      | 10   |      | μA    |  |  |

| R <sub>BFET_DIS</sub>          | BFET Discharge Resistance            |                                                                             |      | 29   |      | kΩ    |  |  |

| Thermal Shutdown (TSD)         |                                      |                                                                             |      |      |      |       |  |  |

| T <sub>SD</sub>                | Thermal Shutdown Threshold           | Temperature rising                                                          |      | 140  |      | °C    |  |  |

| T <sub>SD_HYS</sub>            | Thermal Shutdown Hysteresis          | Temperatsure falling                                                        |      | 30   |      | °C    |  |  |

#### Note:

Rev. 1.0 December 2021 **www.aosmd.com** Page 4 of 13

<sup>1.</sup> Guaranteed by characterization and design.

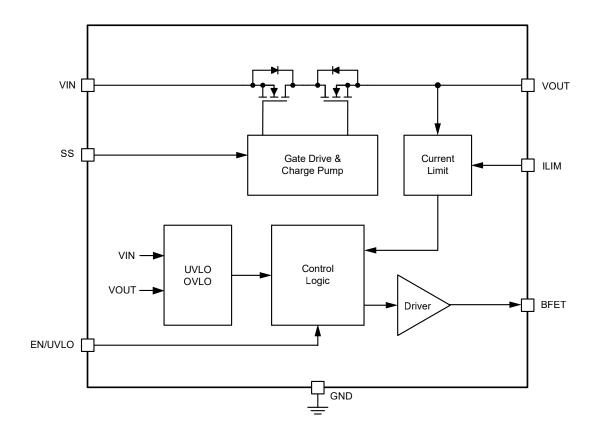

# **Functional Block Diagram**

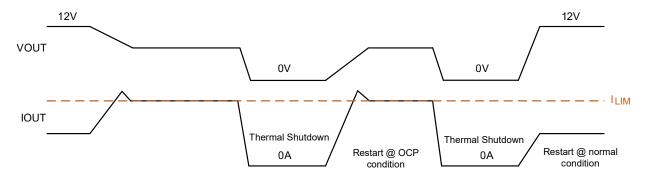

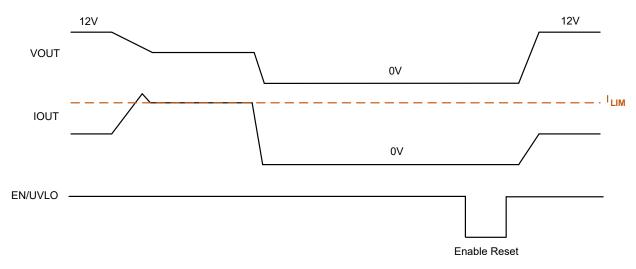

# **Timing Diagrams**

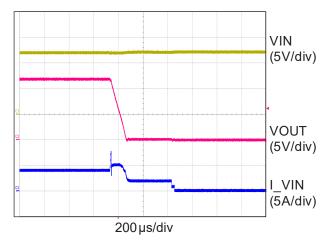

Figure 1. Turn-on Delay, Turn-on and Turn-off Time

Figure 2. Current Limit Operation (AOZ18101-03 Auto-Restart)

Figure 3. Current Limit Operation (AOZ18101-04 Latch-off)

Rev. 1.0 December 2021 www.aosmd.com Page 6 of 13

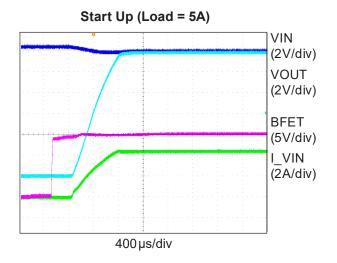

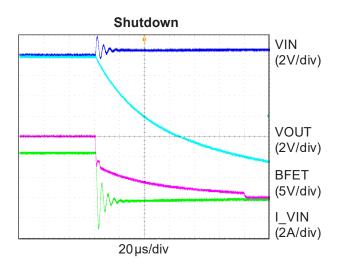

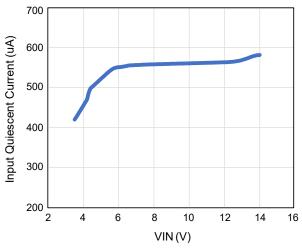

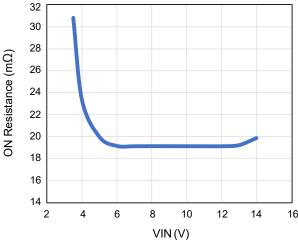

## **Typical Characteristics**

$T_{A} = 25\,^{\circ}\text{C}, \text{ VIN} = 12\,\text{V}, \text{ EN} = 5\,\text{V}, \text{ C}_{_{\text{IN}}} = 10\,\mu\text{F}, \text{ C}_{_{\text{OUT}}} = 10\,\mu\text{F}, \text{ C}_{_{\text{SS}}} = 1\,\text{nF}, \text{ R}_{_{\text{LIM}}} = 150\,\text{k}\Omega, \text{ unless otherwise specified}.$

#### **Over-Current Protection**

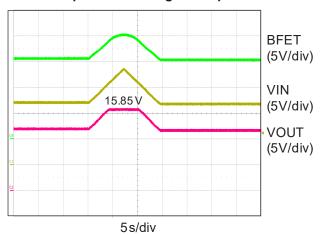

#### **Output Over-Voltage Clamp**

### **Typical Characteristics**

$T_{A} = 25~^{\circ}C,~VIN = 12~V,~EN = 5~V,~C_{IN} = 10~\mu\text{F},~C_{OUT} = 10~\mu\text{F},~C_{SS} = 1~\text{nF},~R_{LIM} = 150~\text{k}\Omega,~unless~otherwise~specified.$

Figure 4. Input Quiescent Current vs. VIN

Figure 6. ON Resistance vs. VIN

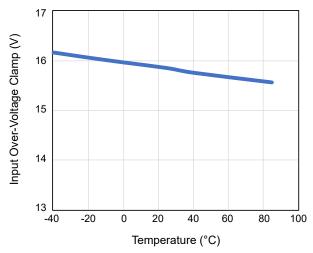

Figure 8. Input Over-Voltage Clamp vs. Temperature

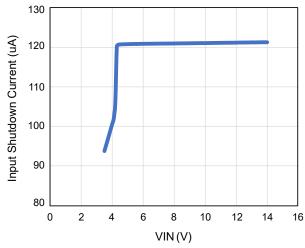

Figure 5. Input Shutdown Current vs. VIN

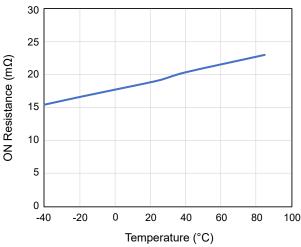

Figure 7. ON Resistance vs. Temperature (VIN = 12V)

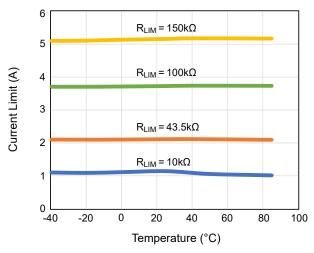

Figure 9. Current Limit vs. Temperature

Rev. 1.0 December 2021 **www.aosmd.com** Page 8 of 13

### **Detailed Description**

AOZ18101DI-03/04 is a current-limiting power switch with under-voltage, over-voltage, over-current and thermal shutdown protections. The VIN and VOUT pins are rated 22 V abs max.

#### **Enable and Under-Voltage Lockout**

The EN/UVLO pin is the ON/OFF control for the power switch. The device is enabled when the voltage at EN/UVLO pin is higher than  $V_{EN\_H}$  and the input voltage is higher than the under-voltage lockout threshold, VIN >  $V_{UVLO\ R}$ .

EN/UVLO pin can be biased with resistor divider network from VIN so that device enable will be tracking the input voltage. While disabled, the AOZ18101DI-03/04 draws 125  $\mu$ A from supply. EN/UVLO cannot be left floating.

#### Input Under-Voltage Lockout (UVLO)

The under-voltage lockout (UVLO) circuit monitors the input voltage. The power switch and the BFET for charging the gate of the external FET are only allowed to turn on when input voltage is higher than UVLO threshold ( $V_{\rm UVLO\_R}$ ). Otherwise the switch is off.

#### **Over-Voltage Clamp (OVC)**

The voltage at VIN pin is constantly monitored once the device is enabled. In case input voltage exceeds the overvoltage clamp ( $V_{\rm OVC}$ ), the output voltage will be clamped at the threshold voltage.

Under the over-voltage clamp (OVC) condition, the output voltage is clamped to the  $V_{OVC}$  level. The power dissipation in the internal FETs under this condition is  $P_{FET\_OVC}$  = (VIN –  $V_{OVC}$ ) x  $I_{OUT}$ , which can heat up the device and causes thermal shutdown when the temperature reaches TSD.

# Programmable Current Limit and Over-Current Protection (OCP)

The AOZ18101DI-03/04 implements current limit to ensure that the current through the switch does not exceed current limit threshold set by the external resistor RLIM.

The current limit threshold can be estimated using the equation below:

$$I_{LIM} = (0.7 + 3 \times 10^{-5} \times R_{LIM})$$

where  $R_{\rm LIM}$  unit is in Ohm and  $I_{\rm LIM}$  unit is in Ampere.

AOZ18101DI-03/04 continuously limits the output current when output is overloaded. Under this condition, the part is dissipating excessive power due to higher voltage drop across VIN to VOUT. If over current continues to exist, it will

reach thermal shutdown threshold and the switch will be turned off.

For AOZ18101DI-03 Auto-Restart version, the power switch will be turn on again to restart after thermal shutdown is released.

For AOZ18101DI-04 Latch Off version, the power switch will only be turned on after toggling the EN/UVLO input logic to reset the device.

The AOZ18101-03/04 integrates a fast comparator which will trigger to turn off the switch at 160% of the current limit threshold set by ILIM pin. After the fast comparator turns off the switch, the switch will be turned on to regulate the current to the set current limit threshold.

#### **Programming Soft Start**

The output soft-start time can be programmed externally through SS pin. The output soft-start time can be estimated using the equations below:

$$t_{ON} = \frac{(C_{SS} + 0.07) \times VIN}{1.067}$$

where  $C_{SS}$  unit is in nF and  $t_{ON}$  unit is in ms.

The SS pin can be left floating ( $C_{SS}$  = open) for the minimum soft-start time (0.75 ms for VIN = 12 V).

The device has internal SOA management to protect the internal FETs. Design Tool is available to select the appropriate  $C_{\rm SS}$  based on load and input voltage.

#### **Blocking FET Driver (BFET)**

When external blocking FET (N-Channel MOSFET) is used, connect BFET pin to the gate of the blocking FET. The BFET pin charges the gate of the external FET when both the voltage at EN/UVLO pin is higher than  $V_{\text{EN}\_H}$  and the input voltage is higher than the under-voltage lockout threshold, VIN >  $V_{\text{UVLO}\_R}.$  The BFET pin discharges current from the gate of the external FET via a  $29\,\text{k}\Omega$  internal discharge resistor, when either the voltage at EN/UVLO pin is lower than  $V_{\text{EN}\_L}$  or the input voltage is lower than the under-voltage lockout threshold, VIN < ( $V_{\text{UVLO}\_R}$ - $V_{\text{UVLO}\_HYS}$ ).

This driver is available for application compatibility if external FET is already placed.

#### Thermal Shutdown Protection (TSD)

Thermal shutdown protects device from excessive temperature. The power switch is turned off when the die temperature reaches thermal shutdown threshold of 140 °C. There is a 30 °C hysteresis. The power switch is allowed to turn on again if die temperature drops below approximately 110 °C.

#### **Input Capacitor Selection**

The input capacitor prevents large voltage transients from appearing at the input, and provides the instantaneous current needed each time the switch turns on to charge output capacitors and to limit input voltage drop. It also prevents high-frequency noise on the power line from passing through to the output. The input capacitor should be located as close to the pin as possible. A minimum of  $10\,\mu\text{F}$  ceramic capacitor should be used. A higher capacitor value is strongly recommended to further reduce the transient voltage drop at the input.

In some applications, a Transient Voltage Suppressor (TVS) can be added on the input side to ensure that the input voltage transients don't exceed the Absolute Maximum Ratings of the device.

#### **Output Capacitor Selection**

The output capacitor acts in a similar way. Also, the output capacitor has to supply enough current for a large load that it may encounter during system transient. This bulk capacitor must be large enough to supply fast transient load in order to prevent the output from dropping.

A Schottky diode can be added between the output and ground to absorb negative voltage spikes

#### **Power Dissipation Calculation**

Calculate the power dissipation for normal load condition using the following equation:

Power Dissipation =  $R_{ON} \times (I_{OUT})^2$

#### **Layout Guidelines**

Good PCB layout is important for improving the thermal and overall performance of AOZ18101DI-03/04. To optimize the switch response time to output short-circuit conditions, keep all traces as short as possible to reduce the effect of unwanted parasitic inductance. Place the input and output bypass capacitors as close as possible to the VIN and VOUT pins. The input and output PCB traces should be as wide as possible. The input and output traces should be sized to carry at least twice the full-load current.

Place a decoupling capacitor as close as possible to the VIN and GND terminals of the device. Minimize the loop area formed by the bypass-capacitor connection, the VIN pins, and the GND pin (EXP) of the IC.

If protective devices such as TVS and Schottky diode are needed, place them physically close to the IC, and route with short traces to reduce inductance.

For the most efficient thermal dissipation, connect the exposed pad to the ground plane with thermal vias as many as possible.

Figure 10 shows example for the AOZ18101DI-03/04 layout. Note that the TVS and the Schoktty diode are optional.

Figure 10. PCB Layout Example

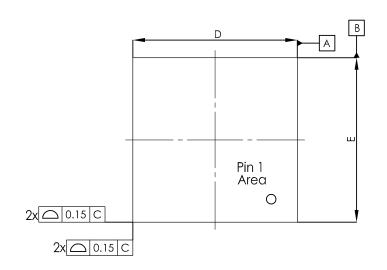

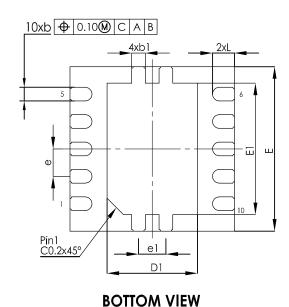

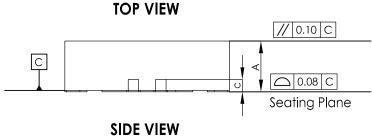

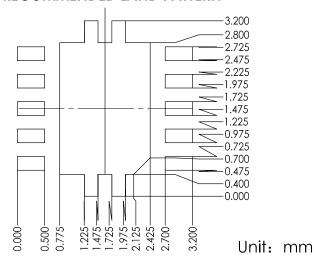

## Package Dimensions, DFN3x3-10L

#### **RECOMMENDED LAND PATTERN**

| SYMBOLS   | DIM. IN MM |      |      | DIM. IN INCH |         |       |

|-----------|------------|------|------|--------------|---------|-------|

| STIVIBULS | MIN.       | NOM. | MAX. | MIN.         | NOM.    | MAX.  |

| Α         | 0.80       | 0.90 | 1.00 | 0.031        | 0.035   | 0.039 |

| A1        | 0.00       |      | 0.05 | 0.000        | 0.000   | 0.002 |

| D         | 2.90       | 3.00 | 3.10 | 0.114        | 0.118   | 0.122 |

| D1        | 1.55       | 1.65 | 1.75 | 0.061        | 0.065   | 0.069 |

| E         | 2.90       | 3.00 | 3.10 | 0.114        | 0.118   | 0.122 |

| E1        | 2.30       | 2.40 | 2.50 | 0.091        | 0.094   | 0.098 |

| L         | 0.30       | 0.40 | 0.50 | 0.012        | 0.016   | 0.020 |

| b         | 0.18       | 0.25 | 0.30 | 0.007        | 0.010   | 0.012 |

| b1        | 0.25REF    |      |      | 0.010REF     |         |       |

| С         | 0.20REF    |      |      | 0.008REF     |         |       |

| е         | 0.50 BSC   |      |      | 0.020 BSC    |         |       |

| e1        | 0.50REF    |      |      |              | 0.02REF |       |

#### NOTE:

- Dimensioning and tolerancing comply with ASME Y14.5M 1994. Controlled dimensions are in milimeters. 1.

- 2. Coplanarity applies to the exposed pad(s) and all termainal leads having metallization.

Rev. 1.0 December 2021 www.aosmd.com Page 11 of 13

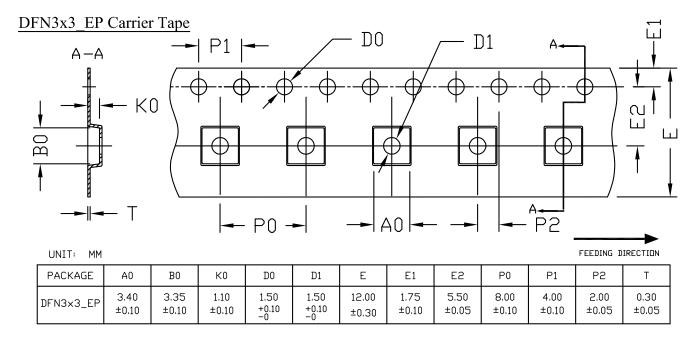

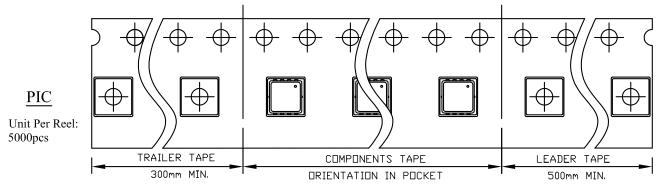

## Tape and Reel Dimensions, DFN3x3-10L

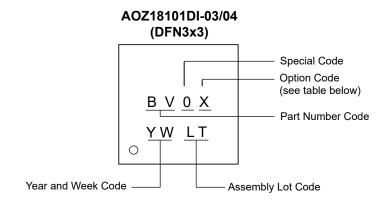

#### **Part Marking**

| Part Number   | Description  | Marking Code |

|---------------|--------------|--------------|

| AOZ18101DI-03 | Auto-Restart | BV03         |

| AOZ18101DI-04 | Latch Off    | BV04         |

#### **LEGAL DISCLAIMER**

Applications or uses as critical components in life support devices or systems are not authorized. AOS does not assume any liability arising out of such applications or uses of its products. AOS reserves the right to make changes to product specifications without notice. It is the responsibility of the customer to evaluate suitability of the product for their intended application. Customer shall comply with applicable legal requirements, including all applicable export control rules, regulations and limitations.

AOS's products are provided subject to AOS's terms and conditions of sale which are set forth at: http://www.aosmd.com/terms\_and\_conditions\_of\_sale

#### LIFE SUPPORT POLICY

ALPHA AND OMEGA SEMICONDUCTOR PRODUCTS ARE NOT AUTHORIZED FOR USE AS CRITICAL COMPONENTS IN LIFE SUPPORT DEVICES OR SYSTEMS.

#### As used herein:

- 1. Life support devices or systems are devices or systems which, (a) are intended for surgical implant into the body or (b) support or sustain life, and (c) whose failure to perform when properly used in accordance with instructions for use provided in the labeling, can be reasonably expected to result in a significant injury of the user.

- 2. A critical component in any component of a life support, device, or system whose failure to perform can be reasonably expected to cause the failure of the life support device or system, or to affect its safety or effectiveness.