# AOZ2234CQI-02

"ollable 28V/10A Synchronous EZBuck™ Regulator

#### **General Description**

The AOZ2234CQI-02 is an I<sup>2</sup>C controllable, high efficiency, easy-to-use DC-DC synchronous buck regulator capable of operation from a 6.5V to 28V input bus. Ability to control the output voltage using the I<sup>2</sup>C bus simplifies converter design for microprocessors or SoCs that require dynamic voltage scaling or voltage margining. The device is capable of supplying 10A of continuous output current with an output voltage adjustable from 1.790625V to 0.6V (±2.0%).

The AOZ2234CQI-02 integrates an internal linear regulator to generate 5.3V  $V_{CC}$  from input. If input voltage is lower than 5.3V, the linear regulator operates at low drop output mode, which allows the  $V_{CC}$  voltage is equal to input voltage minus the drop-output voltage of the internal linear regulator.

A proprietary constant on-time PWM control with input feed-forward results in ultra-fast transient response while maintaining relatively constant switching frequency over the entire input voltage range.

The devices feature multiple protection functions such as  $V_{CC}$  under-voltage lockout, cycle-by-cycle current limit, output over-voltage protection, short-circuit protection, and thermal shutdown.

The AOZ2234CQI-02 is available in a 4mm×4mm QFN-22L package and is rated over a -40°C to +85°C ambient temperature range.

#### **Features**

- Wide input voltage range

- -6.5V to 28V

- 10A continuous output current

- Output voltage adjustable from 0.6V to 1.790625V in 9.375mV

- ±2.0% output voltage accuracy for I<sup>2</sup>C control

- Low R<sub>DS(ON)</sub> internal NFETs

- $-11m\Omega$  high-side

- $-11m\Omega$  low-side

- Constant On-Time with input feed-forward

- Selectable PFM Light-Load Operation

- Ceramic capacitor stable

- Power Good output

- I<sup>2</sup>C address programming

- Integrated bootstrap diode

- Cycle-by-cycle current limit

- Short-circuit protection

- Over voltage protection

- Thermal shutdown

- Thermally enhanced 4mm x 4mm QFN-22L package

#### **Applications**

- Portable computers

- Compact desktop PCs

- Servers

- Graphics cards

- Set-top boxes

- LCD TVs

- Cable modems

- Point-of-load DC/DC converters

- Telecom/Networking/Datacom equipment

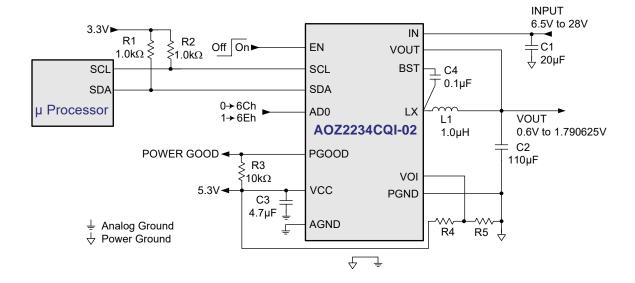

## **Typical Application**

## **Option Table**

| Code           | AD0        | Address<br>(Binary) | Address<br>(Hex) |

|----------------|------------|---------------------|------------------|

| AOZ2234CQI-01  | Ground (0) | 01101000            | 68h              |

| AOLIZZO4GQI-01 | Open (1)   | 01101010            | 6Ah              |

| AOZ2234CQI-02  | Ground (0) | 01101100            | 6Ch              |

| A022234CQI-02  | Open (1)   | 01101110            | 6Eh              |

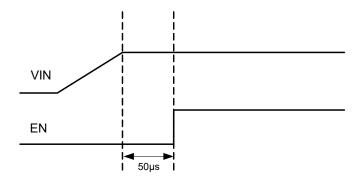

### **Recommended Start-up Sequence**

Rev 1.0 September 2018 www.aosmd.com Page 2 of 23

## **Ordering Information**

| Part Number   | Ambient Temperature Range | Package              | Environmental |  |

|---------------|---------------------------|----------------------|---------------|--|

| AOZ2234CQI-02 | -40°C to +85°C            | 22-Pin 4mm x 4mm QFN | Green Product |  |

AOS Green Products use reduced levels of Halogens, and are also RoHS compliant. Please visit www.aosmd.com/media/AOSGreenPolicy.pdf for additional information.

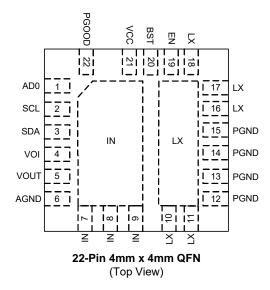

## **Pin Configuration**

## **Pin Description**

| Pin Number         | Pin Name | Pin Function                                                                                                                                                                                                                                                                                                            |

|--------------------|----------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1                  | AD0      | Chip Address. The AD0 pin just connects to AOZ2234CQI-02 VCC pin or GND.                                                                                                                                                                                                                                                |

| 2                  | SCL      | Clock I/O Terminal.                                                                                                                                                                                                                                                                                                     |

| 3                  | SDA      | Data I/O Terminal.                                                                                                                                                                                                                                                                                                      |

| 4                  | VOI      | Initial Output Voltage Feedback Input. Adjust the output voltage with a resistive voltage-divider between VCC and AGND.                                                                                                                                                                                                 |

| 5                  | VOUT     | Output Voltage Feedback Input. Connection to output voltage.                                                                                                                                                                                                                                                            |

| 6                  | AGND     | Analog Ground.                                                                                                                                                                                                                                                                                                          |

| 7, 8, 9            | IN       | Supply Input. IN is the regulator input. All IN pins must be connected together.                                                                                                                                                                                                                                        |

| 10, 11, 16, 17, 18 | LX       | Switching Node.                                                                                                                                                                                                                                                                                                         |

| 12, 13, 14, 15     | PGND     | Power Ground.                                                                                                                                                                                                                                                                                                           |

| 19                 | EN       | Enable Input. The AOZ2234CQI-02 is enabled when EN is pulled high. The device shuts down when EN is pulled low.                                                                                                                                                                                                         |

| 20                 | BST      | Bootstrap Capacitor Connection. The AOZ2234CQI-02 includes an internal bootstrap diode. Connect an external capacitor between BST and LX as shown in Typical Application diagram.                                                                                                                                       |

| 21                 | VCC      | Supply Input for Analog Functions. Bypass VCC to AGND with a 1μF~4.7μF ceramic capacitor. Place the capacitor close to VCC pin.                                                                                                                                                                                         |

| 22 PGOOD           |          | Power Good Signal Output. PGOOD is an open-drain output used to indicate the status of the output voltage. It is internally pulled low when the output voltage is 15% lower than the nominal regulation voltage or 20% higher than the nominal regulation voltage. PGOOD is pulled low during soft-start and shut down. |

Rev 1.0 September 2018 **www.aosmd.com** Page 4 of 23

#### **Absolute Maximum Ratings**

Exceeding the Absolute Maximum Ratings may damage the device.

| Parameter                                        | Rating          |

|--------------------------------------------------|-----------------|

| IN to AGND                                       | -0.3V to 30V    |

| LX to AGND <sup>(1)</sup>                        | -0.3V to 30V    |

| BST to AGND                                      | -0.3V to 36V    |

| PGOOD, EN, VCC, SCL, SDA, VOUT, VOI, AD0 to AGND | -0.3V to 6V     |

| PGND to AGND                                     | -0.3V to +0.3V  |

| Junction Temperature (T <sub>J</sub> )           | +150°C          |

| Storage Temperature (T <sub>S</sub> )            | -65°C to +150°C |

| ESD Rating <sup>(2)</sup>                        | 2kV             |

#### Notes:

- 1. LX to PGND Transient (t<20ns) ----- -7V to  $V_{\mbox{\footnotesize{IN}}}$ +7V.

- 2. Devices are inherently ESD sensitive, handling precautions are required. Human body model rating: 1.5k $\Omega$  in series with 100pF.

#### **Maximum Operating Ratings**

The device is not guaranteed to operate beyond the Maximum Operating ratings.

| Parameter                                                  | Rating             |

|------------------------------------------------------------|--------------------|

| Supply Voltage (V <sub>IN</sub> )                          | 6.5V to 28V        |

| Output Voltage Range                                       | 0.6 V to 1.790625V |

| Ambient Temperature (T <sub>A</sub> )                      | -40°C to +85°C     |

| Package Thermal Resistance $(\theta_{JA})$ $(\theta_{JC})$ | 32°C/W<br>4°C/W    |

#### **Electrical Characteristics**

$T_A$  = 25°C,  $V_{IN}$ =12V, EN = 5V, unless otherwise specified. Specifications in **BOLD** indicate a temperature range of -40°C to +85°C.

| Symbol               | Parameter                                          | Conditions                                                                                                                       | Min.  | Тур.       | Max  | Units            |

|----------------------|----------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------|-------|------------|------|------------------|

| V <sub>IN</sub>      | IN Supply Voltage                                  |                                                                                                                                  | 6.5   |            | 28   | V                |

| V <sub>UVLO</sub>    | Under-Voltage Lockout Threshold of V <sub>CC</sub> | V <sub>CC</sub> rising<br>V <sub>CC</sub> falling                                                                                | 3.7   | 4.2<br>3.9 | 4.4  | V                |

| Iq                   | Quiescent Supply Current of V <sub>CC</sub>        | I <sub>OUT</sub> = 0, V <sub>EN</sub> ≥ 2V, PFM mode                                                                             |       | 0.5        |      | mA               |

| I <sub>OFF</sub>     | Shutdown Supply Current                            | V <sub>EN</sub> = 0V                                                                                                             |       | 1          | 20   | μΑ               |

| V <sub>OUT</sub>     | Output Voltage                                     | $T_A = 25^{\circ}\text{C}, V_{\text{IN}} = 12\text{V}$<br>$V_{\text{OUT}} = 0.6 \text{ to } 1.790625\text{V}, L = 1 \mu\text{H}$ | -2%   | 0%         | 2%   | V <sub>OUT</sub> |

| V <sub>OUT</sub>     | Output Voltage                                     | T <sub>A</sub> = 25°C, V <sub>IN</sub> =12V, V <sub>OUT</sub> =0.9 to<br>1.125V, L=1uH                                           | -1.5% | 0%         | 1.5% | V <sub>OUT</sub> |

| T <sub>r_OUT</sub>   | Output Voltage Rising Time                         | $V_{OUT}$ = 0.9V to 1.3V,<br>$C_{OUT}$ = 88 $\mu$ F, PWM mode                                                                    | 2.5   |            | 15   | μS               |

| T <sub>f_OUT</sub>   | Output Voltage Falling Time                        | V <sub>OUT</sub> = 1.3V to 0.9V,<br>C <sub>OUT</sub> = 88μF, PWM mode                                                            | 2.5   |            | 15   | μS               |

| Enable               |                                                    |                                                                                                                                  |       |            |      |                  |

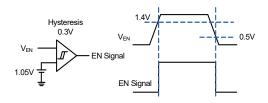

| V <sub>EN</sub>      | EN Input Threshold                                 | Off threshold<br>On threshold                                                                                                    | 1.4   |            | 0.5  | V<br>V           |

| V <sub>EN_HYS</sub>  | EN Input Hysteresis                                |                                                                                                                                  |       | 100        |      | mV               |

| AD0                  |                                                    |                                                                                                                                  |       |            |      |                  |

| V <sub>AD0</sub>     | AD0 Input Threshold                                | Off threshold<br>On threshold                                                                                                    | 4.2   |            | 0.5  | V<br>V           |

| Modulator            |                                                    |                                                                                                                                  |       |            |      |                  |

| f <sub>SW</sub>      | Operating Frequency                                |                                                                                                                                  |       | 400        |      | kHz              |

| T <sub>ON_MIN</sub>  | Minimum On Time                                    |                                                                                                                                  |       | 100        |      | ns               |

| T <sub>ON_MAX</sub>  | Maximum On Time                                    |                                                                                                                                  |       | 2.6        |      | μS               |

| T <sub>OFF_MIN</sub> | Minimum Off Time                                   |                                                                                                                                  |       | 300        |      | ns               |

#### **Electrical Characteristics**

$T_A$  = 25°C,  $V_{IN}$ =12V, EN = 5V, unless otherwise specified. Specifications in **BOLD** indicate a temperature range of -40°C to +85°C.

| Symbol                | Parameter                                    | Conditions                                          | Min.     | Тур.       | Max  | Units  |

|-----------------------|----------------------------------------------|-----------------------------------------------------|----------|------------|------|--------|

| Soft-Start            | ,                                            |                                                     | '        |            |      |        |

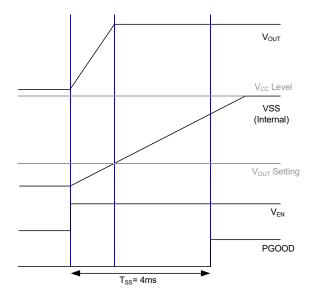

| T <sub>SS_OUT</sub>   | SS Source Time                               | for PGOOD pulled High                               |          | 4          |      | ms     |

| Power Go              | od Signal                                    |                                                     | <u>.</u> |            |      |        |

| V <sub>PG_LOW</sub>   | PGOOD Low Voltage                            | I <sub>OL</sub> = 1mA                               |          |            | 0.5  | V      |

|                       | PGOOD Leakage Current                        |                                                     |          |            | ±1   | μΑ     |

| $V_{PGH}$             | PGOOD Threshold<br>(Low level to High level) | V <sub>OUT</sub> rising                             |          | 90         |      | %      |

| $V_{PGL}$             | PGOOD Threshold<br>(High level to Low level) | V <sub>OUT</sub> rising<br>V <sub>OUT</sub> falling |          | 120<br>85  |      | %<br>% |

|                       | PGOOD Threshold Hysteresis                   |                                                     |          | 5          |      | %      |

| Under Volt            | tage and Over Voltage Protection             |                                                     | <u>.</u> |            |      |        |

| $V_{PL}$              | Under Voltage Threshold                      | V <sub>OUT</sub> falling                            |          | 70         |      | %      |

| T <sub>PL</sub>       | Under Voltage Delay Time                     |                                                     |          | 32         |      | μS     |

| V <sub>PH</sub>       | Over Voltage Threshold                       | V <sub>OUT</sub> rising                             |          | 120        |      | %      |

| Power Sta             | ge Output                                    |                                                     | ·        |            |      |        |

| R <sub>DS(ON)</sub>   | High-Side NFET On-Resistance                 | V <sub>IN</sub> = 12V                               |          | 11         |      | mΩ     |

|                       | High-Side NFET Leakage                       | V <sub>EN</sub> = 0V, V <sub>LX</sub> = 0V          |          |            | 10   | μΑ     |

| R <sub>DS(ON)</sub>   | Low-Side NFET On-Resistance                  | V <sub>LX</sub> = 12V                               |          | 11         |      | mΩ     |

|                       | Low-Side NFET Leakage                        | V <sub>EN</sub> = 0V                                |          |            | 10   | μΑ     |

| V <sub>CC</sub> Outpu | ıt                                           |                                                     |          |            |      |        |

| V <sub>CC</sub>       | V <sub>CC</sub> output voltage               | $V_{IN} \ge 6.5V$ , $I_{CC} = 0mA$                  | 5.09     | 5.3        | 5.51 | V      |

| I <sub>CC</sub>       | V <sub>CC</sub> current limit                | V <sub>IN</sub> ≥ 6.5V                              | 50       |            |      | mA     |

| Over-curre            | ent and Thermal Protection                   |                                                     |          |            |      |        |

| I <sub>LIM</sub>      | Current Limit                                |                                                     | 15       |            |      | Α      |

|                       | Thermal Shutdown Threshold                   | T <sub>J</sub> rising<br>T <sub>J</sub> falling     |          | 150<br>100 |      | °C     |

Rev 1.0 September 2018 **www.aosmd.com** Page 6 of 23

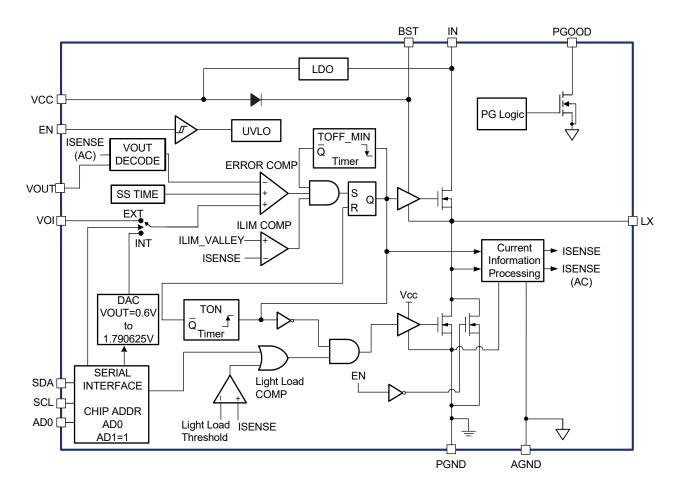

## **Functional Block Diagram**

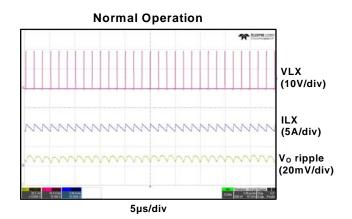

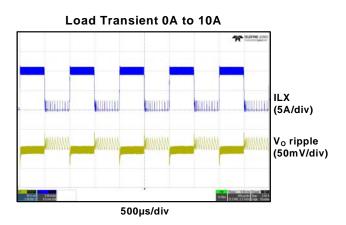

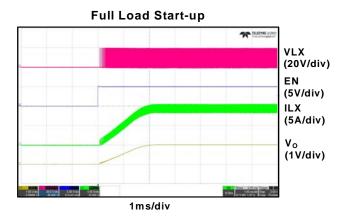

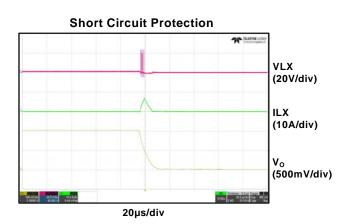

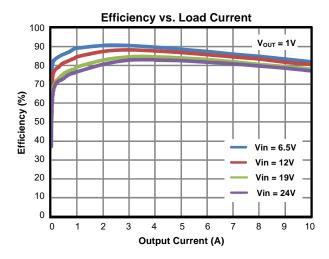

## **Typical Performance Characteristics**

Circuit of Typical Application.  $T_A$  = 25°C,  $V_{IN}$  = 19V,  $V_{OUT}$  = 1V, fs = 400kHz unless otherwise specified.

Rev 1.0 September 2018 **www.aosmd.com** Page 8 of 23

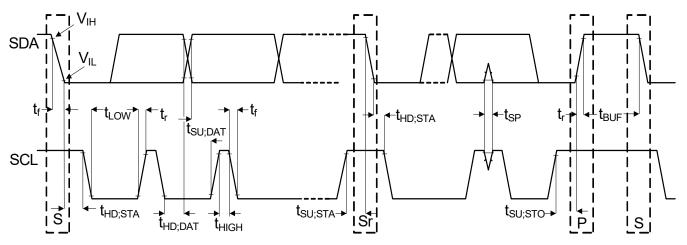

## I<sup>2</sup>C Control Specification<sup>(3)(4)(5)</sup>

| Symbol              | Parameter                                               | Conditions | Min.                 | Тур. | Max | Units |

|---------------------|---------------------------------------------------------|------------|----------------------|------|-----|-------|

| V <sub>IL</sub>     | Low level input voltage                                 |            |                      |      | 0.6 | V     |

| V <sub>IH</sub>     | High level input voltage                                |            | 2.9                  |      |     | V     |

| V <sub>hys</sub>    | Hysteresis of Schmitt trigger inputs                    |            | 0.11                 |      |     | V     |

| V <sub>OL</sub>     | Low level output voltage (Open drain, 3mA sink current) |            |                      |      | 0.4 | V     |

| T <sub>SP</sub>     | Pulse width of spikes suppressed by input filter        |            | 32                   |      |     | ns    |

| f <sub>SCL</sub>    | SCL clock frequency                                     |            |                      |      | 400 | kHz   |

| t <sub>HD;STA</sub> | Hold time (repeated), START condition                   |            | 0.6                  |      |     | μs    |

| t <sub>LOW</sub>    | Low period of SCL clock                                 |            | 1.3                  |      |     | μS    |

| t <sub>HIGH</sub>   | High period of SCL clock                                |            | 0.6                  |      |     | μS    |

| t <sub>SU;STA</sub> | Set-up time for a repeated START condition              |            | 0.6                  |      |     | μS    |

| t <sub>HD;DAT</sub> | Data hold time                                          |            | 50                   |      | 900 | ns    |

| t <sub>SU;DAT</sub> | Data set-up time                                        |            | 100                  |      |     | ns    |

| t <sub>r</sub>      | Rise time (SDA or SCL)                                  |            | 20+0.1C <sub>b</sub> |      | 300 | ns    |

| t <sub>f</sub>      | Fall time (SDA or SCL)                                  |            | 5+0.1C <sub>b</sub>  |      | 300 | ns    |

| t <sub>SU;STO</sub> | Set-up time for STOP condition                          |            | 0.6                  |      |     | μS    |

| t <sub>BUF</sub>    | Bus free time between STOP and START conditions         |            | 1.3                  |      |     | μS    |

| C <sub>b</sub>      | Capacitive load for each bus line                       |            |                      |      | 400 | pF    |

| I <sub>d</sub>      | SDA driver capability                                   |            | 25                   |      | 100 | mA    |

#### Notes:

- 3. Ensured by design. Not production tested.

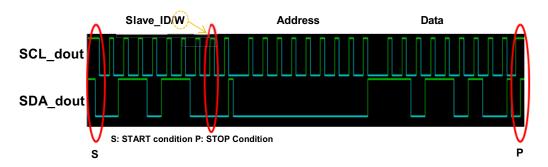

- 4. Refer to Figure 1 for I<sup>2</sup>C timing definitions.

- 5. C<sub>b</sub> = capacitance of bus line in pF.

Figure 1. I<sup>2</sup>C Timing Definitions

Rev 1.0 September 2018 **www.aosmd.com** Page 9 of 23

## I<sup>2</sup>C Register Maps

| Register<br>Name  | Register<br>Address | Bit 7            | Bit6                 | Bit 5 | Bit 4                       | Bit 3 | Bit 2 | Bit 1 | Bit 0              |

|-------------------|---------------------|------------------|----------------------|-------|-----------------------------|-------|-------|-------|--------------------|

| Output<br>Voltage | 00                  | Odd Parity       | Output Voltage [6:0] |       |                             |       |       |       |                    |

| Control A         | 01                  | Internal<br>Mode |                      |       | Output<br>Voltage<br>Change | PFMb  |       |       | Protection<br>Mode |

## Summary of Default Control Bits<sup>(6)</sup>

| Control Bit(s)           | Default           | Function                                                                                                                                                                                                                                                                  |

|--------------------------|-------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| VOUT [6:0]               | 0110010           | VOUT code, 7 bits VOUT [6:0]. Part default to 1.068750V.                                                                                                                                                                                                                  |

| Internal Mode            | 0 (External Mode) | 0 case: External Mode 1 case: Internal Mode (1). If set to 1, the part switches to internal mode and VOUT register value controls output voltage. (2). The part can be set back to external control mode at any time by wiring this bit to 0.                             |

| Output Voltage<br>Change | 0                 | 0 case: Internal protection on 1 case: Internal protection off (1). If set to 0, when VOUT code change, the internal protection isn't turned off. (2). If set to 1, when VOUT code change, the internal protection is turned off to avoid triggering internal protection. |

| PFMb                     | 1                 | Select PFM or PWM at light load. 0 case: PFM 1 case: PWM Part defaults to PWM.                                                                                                                                                                                            |

| Protection Mode          | 1                 | Select Latch-off or Auto-recovery for protection.  0 case: Auto-recovery mode  1 case: Latch-off mode  Part defaults to Latch-off mode.                                                                                                                                   |

#### Note:

- When the system satisfies any of the following conditions, the I<sup>2</sup>C register will reset to default settings:

- (1) No input voltage

- (2) LDO VCC is less than VCC UVLO falling threshold

- (3) EN signal is disabled

#### **Odd Parity Bit**

The odd parity bit is set by the Master controller to be the exclusive-NOR of the output voltage [6:0] bits. It will be used by the AOZ2234CQI-02 to check that a valid data byte has been received. If odd parity is not equal to the exclusive-NOR of the output voltage [6:0] bits, the

AOZ2234CQI-02 assumes that an error has been occurred during the data transmission, and it will not send an ACK bit, nor will it reset the VOUT to the received code. (or, if the Control register will not reset the register contents as requested). The Master should try again to re-send the data. When reading back the VOUT register, the parity bit is sent back.

Rev 1.0 September 2018 **www.aosmd.com** Page 10 of 23

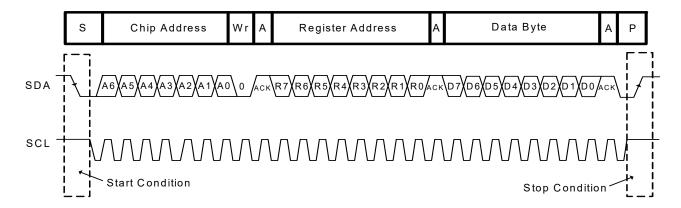

## I<sup>2</sup>C Serial Interface Description

The AOZ2234CQI-02 serial data interface works as an  $I^2C$  slave device. It supports most standard data transfer mode (100kbps) and fast transfer mode (400kbps). The serial interface provides the mean to program a precision resistor DAC to set up a VID output voltage control for the 10A DC/DC converter. A one-byte data is written by the  $I^2C$  Master to the AOZ2234CQI-02 and stored in a data buffer for the VID. The content of the data buffer can also be read back by the Master.

After I<sup>2</sup>C is enabled, the AOZ2234CQI-02 starts to check the address code sent by the Master every time a START condition is detected. If a valid address code, AD[6:0], is recognized, it will send out an ACK bit by pulling down on the SDA bus during the clock pulse 9 of the SCL bus. The ACK time of the clock pulse 9 of the SCL bus can be written as below.

$$T_{ACK} = 9 \times \frac{1}{f_{SCL}}$$

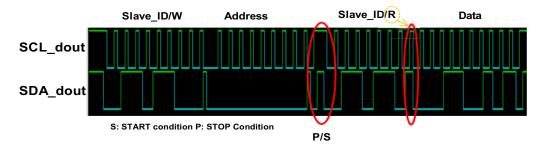

Figure 2. A Complete Write Byte Transfer

Figure 3. Single Read

Figure 4. Single Write

Rev 1.0 September 2018 **www.aosmd.com** Page 11 of 23

If no valid address is detected, no action will be taken and no ACK sent will be sent. The I<sup>2</sup>C controller assumes the address is for other I<sup>2</sup>C devices and it will ignore the data bits and resume the search for the next valid address transfer. Finally, the response time from entering command to changing internal function is shown as below:

$$T_R = 27 \times \frac{1}{f_{SCL}}$$

After a valid address code is confirmed, the next bit (Wr) is checked for Write ("0") or Read ("1") mode. If the requested operation is Write mode, the AOZ2234CQI-02 will evaluate the data codeD[7:0], received after the address ACK.

Once the write data is validated, AOZ2234CQI-02 will send ACK on the SDA bus. The data code will also be transferred to the data holding buffer of the VID and the output voltage will move to the new, or ideal, value. If the data is not valid, no ACK will be sent. It will be up to the I<sup>2</sup>C Master to repeat the operation.

If the requested operation is Read mode, the AOZ2234CQI-02 will transmit the content of the VID data buffer register, or D[7:0], on the SDA bus. After the 8 data bits are transmitted and STOP detected, the AOZ2234CQI-02 will return to the normal operation regardless of ACK is received or not. It will be up to the I<sup>2</sup>C Master to re-send a Read request if the last Read operation is deemed invalid.

#### **Detailed Description**

The AOZ2234CQI-02 is a high-efficiency, easy-to-use, synchronous buck regulator with a voltage scaling control to power up MCUs requiring core voltage tune-ups. After the initial power up, the output voltage can be programmed/scaled by VID codes sent over an I<sup>2</sup>C compatible bus. The regulator is capable of supplying 10A of continuous output current with an output voltage adjustable from 0.6V to 1.790625V.

The input voltage of AOZ2234CQI-02 can be as low as 6.5V. The highest input voltage of AOZ2234CQI-02 can be 28V. Constant on-time PWM with input feed-forward control scheme results in ultra-fast transient response while maintaining relatively constant switching frequency over the entire input range. True AC current mode control scheme guarantees the regulator can be stable with ceramics output capacitor. Protection features include  $V_{CC}$  under-voltage lockout, cycle-by-cycle current limit, output over voltage and under voltage protection, short-circuit protection, and thermal shutdown.

The AOZ2234CQI-02 is available in 22-pin 4mm×4mm QFN package.

#### Input Power Architecture

The AOZ2234CQI-02 integrates an internal linear regulator to generate 5.3V ( $\pm 5\%$ ) V<sub>CC</sub> from input. If input voltage is lower than 5.3V, the linear regulator operates at low drop-output mode; the V<sub>CC</sub> voltage is equal to input voltage minus the drop-output voltage of internal linear regulator.

#### **Enable and Soft Start**

The AOZ2234CQI-02 has internal soft start feature to limit in-rush current and ensure the output voltage ramps up smoothly to regulate voltage. A soft start process begins when  $V_{CC}$  rises to 4.2V and voltage on EN pin is HIGH. The output voltage follows the internal voltage of soft-start ( $V_{SS}$ ) when it is lower than initial output voltage. When  $V_{SS}$  is higher than initial output voltage, the voltage of VOUT pin is regulated by internal precise band-gap voltage. Moreover, the soft start period between EN and PGOOD is 4ms.The soft start sequence of AOZ2234CQI-02 is shown in Figure 5.

Figure 5. Soft Start Sequence of AOZ2234CQI-02

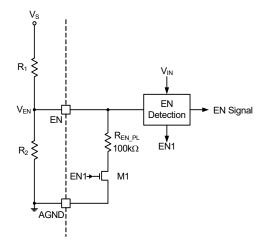

#### **Enable**

The AOZ2234CQI-02 has an embedded discharge path, including a  $100k\Omega$  resistor and a NMOS device, M1. This discharge path is activated when input voltage  $V_{IN}$  is high and EN voltage  $V_{en}$  is low. The internal circuits of EN pin is shown in Figure 6.

Figure 6. Enable Internal Circuit

There are two different enable control methods:

- 1. Connection to EN pin by an external resistive voltage divider.

- 2. Direct connection to EN pin by an external power source, V<sub>s</sub>.

Rev 1.0 September 2018 **www.aosmd.com** Page 13 of 23

In the first condition, we must consider the internal pull-down resistance by using a divider circuit with an external power source  $V_s$  to get  $V_{EN}$ . The  $V_{EN}$  can be calculated by the following formula:

$$V_{EN} = \frac{R_2 /\!/ R_{EN\_PL}}{R_1 + (R_2 /\!/ R_{EN\_PL})} \times V_s$$

When the  $V_{IN}$  is high and the  $V_{EN}$  is high, the EN internal M1 is turned off, and then the pull down resistance is removed for  $V_{EN}$ , the  $V_{EN}$  can be re-calculated by:

$$V_{EN} = \frac{R_2}{R_1 + R_2} \times V_s$$

In the second condition, the AOZ2234CQI-02 will be turned on when the  $V_{EN}$  is higher than 1.4V, and will be turned off when the  $V_{EN}$  is lower than 0.5V. The simplified schematic and timing sequence are shown in Figure 7.

Figure 7. Enable Threshold Schematic and Timing Sequence

## Constant-On-Time PWM Control with Input Feed-Forward

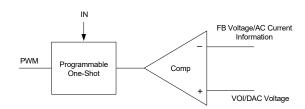

The control algorithm of AOZ2234CQI-02 is constant-ontime PWM control with input feed-forward. The simplified control schematic is shown in Figure 8. The high-side switch on time is determined solely by a one-shot whose pulse width is inversely proportional to input voltage (IN). The one-shot is triggered when the internal VOI/DAC voltage is higher than the combined information of output voltage and the AC current information of inductor, which is processed and obtained through the sensed low-side MOSFET current once it turns-on. The added AC current information can help the stability of constant-on time control even with pure ceramic output capacitors, which have very low ESR. The AC current information has no DC offset, which does not cause offset with output load change, which is fundamentally different from other V<sup>2</sup> constant-on time control schemes.

Figure 8. Simplified Control Schematic

#### **True Current Mode Control**

The constant-on-time control scheme is intrinsically unstable if output capacitor's ESR is not large enough as an effective current-sense resistor. Ceramic capacitors usually cannot be used as output capacitor.

The AOZ2234CQI-02 senses the low-side MOSFET current and processes it into DC current and AC current information using AOS proprietary technique. The AC current information is decoded and added on the VOUT pin on phase. With AC current information, the stability of constant-on-time control is significantly improved even without the help of output capacitor's ESR; and thus, the pure ceramic capacitor solution can be applicant. The pure ceramic capacitor solution can significantly reduce the output ripple (no ESR caused overshoot and undershoot) and less board area design.

#### **Current-Limit Protection**

The AOZ2234CQI-02 has the current-limit protection by using  $R_{\rm DS(ON)}$  of the low-side MOSFET to be as current sensing. To detect real current information, a minimum constant-off time (300ns typical) is implemented after a constant-on time. If the current exceeds the current-limit threshold, the PWM controller is not allowed to initiate a new cycle. The actual peak current is greater than the current-limit threshold by an amount equal to the inductor ripple current. Therefore, the exact current-limit characteristic and maximum load capability are a function of the inductor value and input and output voltages. The current limit will keep the low-side MOSFET on and will not allow another high-side on-time, until the current limit.

After 16 switching cycles, the AOZ2234CQI-02 considers this is a true failed condition and thus, turns-off both high-side and low-side MOSFETs and latches off. Only when triggered, the enable can restart the AOZ2234CQI-02 again.

**Table 1: Output Voltage Setting vs Register Code**

| Code | Binary  | VOOUT    | Code | Binary  | VOUT     | Code | Binary  | VOUT     | Code | Binary  | VOUT     |

|------|---------|----------|------|---------|----------|------|---------|----------|------|---------|----------|

| 0    | 0000000 | 0.600000 | 32   | 0100000 | 0.900000 | 64   | 1000000 | 1.200000 | 96   | 1100000 | 1.500000 |

| 1    | 0000001 | 0.609375 | 33   | 0100001 | 0.909375 | 65   | 1000001 | 1.209375 | 97   | 1100001 | 1.509375 |

| 2    | 0000010 | 0.618750 | 34   | 0100010 | 0.918750 | 66   | 1000010 | 1.218750 | 98   | 1100010 | 1.518750 |

| 3    | 0000011 | 0.628125 | 35   | 0100011 | 0.928125 | 67   | 1000011 | 1.228125 | 99   | 1100011 | 1.528125 |

| 4    | 0000100 | 0.637500 | 36   | 0100100 | 0.937500 | 68   | 1000100 | 1.237500 | 100  | 1100100 | 1.537500 |

| 5    | 0000101 | 0.646875 | 37   | 0100101 | 0.946875 | 69   | 1000101 | 1.246875 | 101  | 1100101 | 1.546875 |

| 6    | 0000110 | 0.656250 | 38   | 0100110 | 0.956250 | 70   | 1000110 | 1.256250 | 102  | 1100110 | 1.556250 |

| 7    | 0000111 | 0.665625 | 39   | 0100111 | 0.965625 | 71   | 1000111 | 1.265625 | 103  | 1100111 | 1.565625 |

| 8    | 0001000 | 0.675000 | 40   | 0101000 | 0.975000 | 72   | 1001000 | 1.275000 | 104  | 1101000 | 1.575000 |

| 9    | 0001001 | 0.684375 | 41   | 0101001 | 0.984375 | 73   | 1001001 | 1.284375 | 105  | 1101001 | 1.584375 |

| 10   | 0001010 | 0.693750 | 42   | 0101010 | 0.993750 | 74   | 1001010 | 1.293750 | 106  | 1101010 | 1.593750 |

| 11   | 0001011 | 0.703125 | 43   | 0101011 | 1.003125 | 75   | 1001011 | 1.303125 | 107  | 1101011 | 1.603125 |

| 12   | 0001100 | 0.712500 | 44   | 0101100 | 1.012500 | 76   | 1001100 | 1.312500 | 108  | 1101100 | 1.612500 |

| 13   | 0001101 | 0.721875 | 45   | 0101101 | 1.021875 | 77   | 1001101 | 1.321875 | 109  | 1101101 | 1.621875 |

| 14   | 0001110 | 0.731250 | 46   | 0101110 | 1.031250 | 78   | 1001110 | 1.331250 | 110  | 1101110 | 1.631250 |

| 15   | 0001111 | 0.740625 | 47   | 0101111 | 1.040625 | 79   | 1001111 | 1.340625 | 111  | 1101111 | 1.640625 |

| 16   | 0010000 | 0.750000 | 48   | 0110000 | 1.050000 | 80   | 1010000 | 1.350000 | 112  | 1110000 | 1.650000 |

| 17   | 0010001 | 0.759375 | 49   | 0110001 | 1.059375 | 81   | 1010001 | 1.359375 | 113  | 1110001 | 1.659375 |

| 18   | 0010010 | 0.768750 | 50   | 0110010 | 1.068750 | 82   | 1010010 | 1.368750 | 114  | 1110010 | 1.668750 |

| 19   | 0010011 | 0.778125 | 51   | 0110011 | 1.078125 | 83   | 1010011 | 1.378125 | 115  | 1110011 | 1.678125 |

| 20   | 0010100 | 0.787500 | 52   | 0110100 | 1.087500 | 84   | 1010100 | 1.387500 | 116  | 1110100 | 1.687500 |

| 21   | 0010101 | 0.796875 | 53   | 0110101 | 1.096875 | 85   | 1010101 | 1.396875 | 117  | 1110101 | 1.696875 |

| 22   | 0010110 | 0.806250 | 54   | 0110110 | 1.106250 | 86   | 1010110 | 1.406250 | 118  | 1110110 | 1.706250 |

| 23   | 0010111 | 0.815625 | 55   | 0110111 | 1.115625 | 87   | 1010111 | 1.415625 | 119  | 1110111 | 1.715625 |

| 24   | 0011000 | 0.825000 | 56   | 0111000 | 1.125000 | 88   | 1011000 | 1.425000 | 120  | 1111000 | 1.725000 |

| 25   | 0011001 | 0.834375 | 57   | 0111001 | 1.134175 | 89   | 1011001 | 1.434375 | 121  | 1111001 | 1.734375 |

| 26   | 0011010 | 0.843750 | 58   | 0111010 | 1.143750 | 90   | 1011010 | 1.443750 | 122  | 1111010 | 1.743750 |

| 27   | 0011011 | 0.853125 | 59   | 0111011 | 1.153125 | 91   | 1011011 | 1.453125 | 123  | 1111011 | 1.753125 |

| 28   | 0011100 | 0.862500 | 60   | 0111100 | 1.162500 | 92   | 1011100 | 1.462500 | 124  | 1111100 | 1.762500 |

| 29   | 0011101 | 0.871875 | 61   | 0111101 | 1.171875 | 93   | 1011101 | 1.471875 | 125  | 1111101 | 1.771875 |

| 30   | 0011110 | 0.881250 | 62   | 0111110 | 1.181250 | 94   | 1011110 | 1.481250 | 126  | 1111110 | 1.781250 |

| 31   | 0011111 | 0.890625 | 63   | 0111111 | 1.190625 | 95   | 1011111 | 1.490625 | 127  | 1111111 | 1.790625 |

Rev 1.0 September 2018 **www.aosmd.com** Page 15 of 23

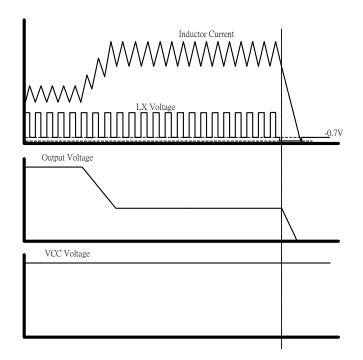

Figure 9. OCP Timing Chart

#### **Output Voltage Under-Voltage Protection**

If the output voltage is lower than 70% by over-current or short circuit, AOZ2234CQI-02 will wait for 32us(typical) and turns-off both high-side and low-side MOSFETs and latches off. Only when triggered, the enable can restart the AOZ2234CQI-02 again.

#### **Output Voltage Over-Voltage Protection**

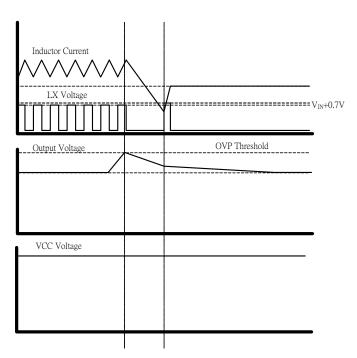

The threshold of OVP is set 20% higher than VOI/DAC voltage. When the voltage of VOUT pin exceeds the OVP threshold, high-side MOSFET is turned-off and low-side MOSFETs is turned-on until the voltage of VOUT pin is lower than VOI/DAC voltage.

Figure 10. OVP Timing Chart

#### **Output Voltage Registers**

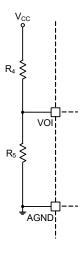

The AOZ2234CQI-02 has 7 bits of output voltage register control for output voltage adjusting from 0.6V to 1.790625V. Output Voltage Setting vs Register Code shows the output voltage setting for DAC voltage and register codes. When the AOZ2234CQI-02 powers up, the startup and output voltage regulation conditions are set by the external resistor divider feedback to the VOI pin from VCC voltage. Therefore, the initial output voltage can be calculated by:

$$VOI = \frac{R_5}{R_4 + R_5} \bullet V_{CC}$$

Figure 11. VOI Divided Circuit

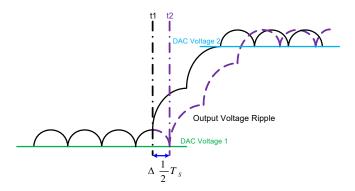

#### **Output Voltage Rising and Falling Time**

We can adjust AOZ2234CQI-02's output voltage level by the I2C interface. The output voltage rising time and falling time is determined by our internal slew-rate control circuit. Resulted from various output voltage change points, it makes different rising and falling time. If the output voltages tarts to change at the peak of output voltage, it takes less time to achieve new output voltage level than from the valley. The difference of their rising time in the same sample is approximately 1/2 of switching cycle time.

Figure 12. Variations of Output Voltage Rising Time

#### **Application Information**

The basic AOZ2234CQI-02 application circuit is shown in Typical Application section. The component selection is explained below.

#### Input capacitor

The input capacitor must be connected to the IN pins and PGND pin of the AOZ2234CQI-02 to maintain steady input voltage and filter out the pulsing input current. A small decoupling capacitor, usually 4.7uF, should be connected to the  $V_{CC}$  pin and AGND pin for stable operation of the AOZ2234CQI-02. The voltage rating of input capacitor must be greater than maximum input voltage plus ripple voltage.

The input ripple voltage can be approximated by equation below:

$$\Delta V_{IN} = \frac{I_O}{f \times C_{IN}} \times \left(1 - \frac{V_O}{V_{IN}}\right) \times \frac{V_O}{V_{IN}}$$

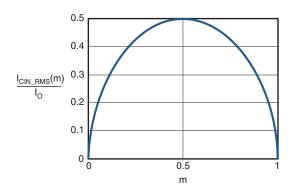

Since the input current is discontinuous in a buck converter, the current stress on the input capacitor is another concern when selecting the capacitor. For a buck circuit, the RMS value of input capacitor current can be calculated by:

$$I_{CIN\_RMS} = I_O \times \sqrt{\frac{V_O}{V_{IN}} \left(1 - \frac{V_O}{V_{IN}}\right)}$$

if let *m* equal the conversion ratio:

$$\frac{V_O}{V_{IN}} = m$$

The relation between the input capacitor RMS current and voltage conversion ratio is calculated and shown in Figure 13. It can be seen that when  $V_O$  is half of  $V_{IN}$ ,  $C_{IN}$  is under the worst current stress. The worst current stress on  $C_{IN}$  is  $0.5 \cdot I_O$ .

Figure 13. I<sub>CIN</sub> vs. Voltage Conversion Ratio

For reliable operation and best performance, the input capacitors must have current rating higher than I<sub>CIN-RMS</sub> at worst operating conditions. Ceramic capacitors are preferred for input capacitors because of their low ESR and high ripple current rating. Depending on the application circuits, other low ESR tantalum capacitor or aluminum electrolytic capacitor may also be used. When selecting ceramic capacitors, X5R or X7R type dielectric ceramic capacitors are preferred for their better temperature and voltage characteristics. Note that the ripple current rating from capacitor manufactures is based on certain amount of life time. Further de-rating may be necessary for practical design requirement.

#### Inductor

The inductor is used to supply constant current to output when it is driven by a switching voltage. For given input and output voltage, inductance and switching frequency together decide the inductor ripple current, which is:

$$\Delta I_L = \frac{V_O}{f \times L} \times \left(1 - \frac{V_O}{V_{IN}}\right)$$

Rev 1.0 September 2018 **www.aosmd.com** Page 17 of 23

The peak inductor current is:

$$I_{Lpeak} = I_O + \frac{\Delta I_L}{2}$$

High inductance gives low inductor ripple current but requires larger size inductor to avoid saturation. Low ripple current reduces inductor core losses. It also reduces RMS current through inductor and switches, which results in less conduction loss. Usually, peak to peak ripple current on inductor is designed to be 30% to 50% of output current.

When selecting the inductor, make sure it is able to handle the peak current without saturation even at the highest operating temperature.

The inductor takes the highest current in a buck circuit. The conduction loss on inductor needs to be checked for thermal and efficiency requirements.

Surface mount inductors in different shape and styles are available from Coilcraft, Elytone and Murata. Shielded inductors are small and radiate less EMI noise. But they cost more than unshielded inductors. The choice depends on EMI requirement, price and size.

#### **Output Capacitor**

The output capacitor is selected based on the DC output voltage rating, output ripple voltage specification and ripple current rating.

The selected output capacitor must have a higher rated voltage specification than the maximum desired output voltage including ripple. De-rating needs to be considered for long term reliability.

Output ripple voltage specification is another important factor for selecting the output capacitor. In a buck converter circuit, output ripple voltage is determined by inductor value, switching frequency, output capacitor value and ESR. It can be calculated by the equation below:

$$\Delta V_o = \Delta I_L \times (ESR_{CO} + \frac{1}{8 \times f \times C_o})$$

where,  $C_O$  is output capacitor value and  $ESR_{CO}$  is the Equivalent Series Resistor of output capacitor.

When low ESR ceramic capacitor is used as output capacitor, the impedance of the capacitor at the switching frequency dominates. Output ripple is mainly caused by capacitor value and inductor ripple current. The output ripple voltage calculation can be simplified to:

$$\Delta V_{O} = \Delta I_{L} \times \frac{1}{8 \times f \times C_{O}}$$

If the impedance of ESR at switching frequency dominates, the output ripple voltage is mainly decided by capacitor ESR and inductor ripple current. The output ripple voltage calculation can be further simplified to:

$$\Delta V_{O} = \Delta I_{I} \times ESR_{CO}$$

For lower output ripple voltage across the entire operating temperature range, X5R or X7R dielectric type of ceramic, or other low ESR tantalum are recommended to be used as output capacitors.

In a buck converter, output capacitor current is continuous. The RMS current of output capacitor is decided by the peak to peak inductor ripple current. It can be calculated by:

$$I_{CO\_RMS} = \frac{\Delta I_L}{\sqrt{12}}$$

Usually, the ripple current rating of the output capacitor is a smaller issue because of the low current stress. When the buck inductor is selected to be very small and inductor ripple current is high, output capacitor could be overstressed.

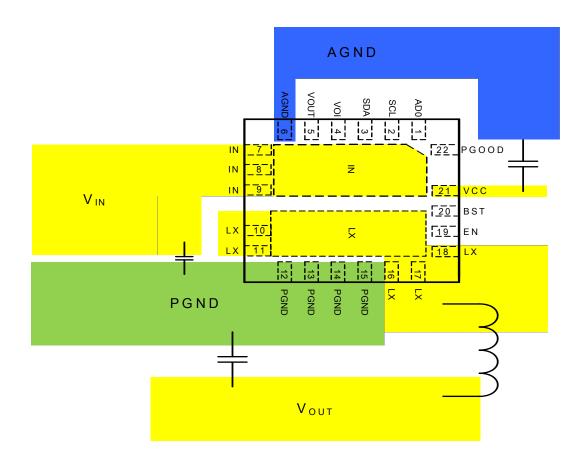

## Thermal Management and Layout Consideration

In the AOZ2234CQI-02 buck regulator circuit, high pulsing current flows through two circuit loops. The first loop starts from the input capacitors, to the IN pin, to the LX pins, to the filter inductor, to the output capacitor and load, and then return to the input capacitor through ground. Current flows in the first loop when the high side switch is on. The second loop starts from inductor, to the output capacitors and load, to the low side switch. Current flows in the second loop when the low side switch is on.

In PCB layout, minimizing the two loops area reduces the noise of this circuit and improves efficiency. A ground plane is strongly recommended to connect input capacitor, output capacitor, and PGND pin of the AOZ2234CQI-02.

In the AOZ2234CQI-02 buck regulator circuit, the major power dissipating components are the AOZ2234CQI-02 and the output inductor. The total power dissipation of converter circuit can be measured by input power minus output power.

$$P_{total\_loss} = V_{IN} \times I_{IN} - V_{O} \times I_{O}$$

The power dissipation of inductor can be approximately calculated by DCR of inductor and output current.

$$P_{inductor\ loss} = I_0^2 \times R_{inductor} \times 1.1$$

The actual junction temperature can be calculated with power dissipation in the AOZ2234CQI-02 and thermal impedance from junction to ambient.

$$T_{iunction} = (P_{total\ loss} - P_{inductor\ loss}) \cdot \Theta_{JA} + T_A$$

The maximum junction temperature of AOZ2234CQI-02 is 150°C, which limits the maximum load current capability.

The thermal performance of the AOZ2234CQI-02 is strongly affected by the PCB layout. Extra care should be taken by users during design process to ensure that the IC will operate under the recommended environmental conditions.

#### **Layout Considerations**

Several layout tips are listed below for the best electric and thermal performance.

- Connected a small copper plane to LX pin to have lower noise interference area.

- The IN pins and pad are connected to internal high side switch drain. They are also low resistance thermal conduction path. Connected a large copper plane to IN pins to help thermal dissipation.

- Input capacitors should be connected to the IN pin and the PGND pin as close as possible to reduce the switching spikes.

- 4. Decoupling capacitor  $C_{VCC}$  should be connected to  $V_{CC}$  and AGND as close as possible.

- 5. Keep sensitive signal traces such as output trace far away from the LX pins.

- 6. Let digital pins such as AD0, SCL and SDA, to use AGND.

- 7. Let VOI pin to use AGND.

- Pour copper plane on all unused board area and connect it to stable DC nodes, like VIN, GND or VOUT.

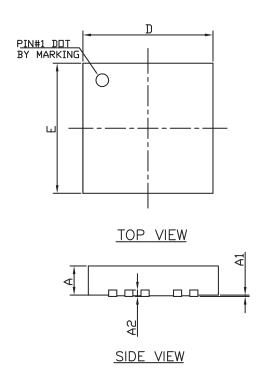

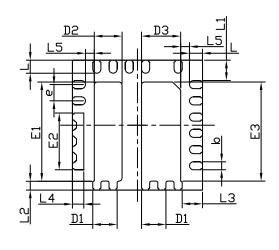

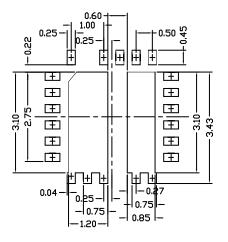

### Package Dimensions, QFN4x4-22L, EP2\_S

BOTTOM VIEW

#### RECOMMENDED LAND PATTERN

UNIT: mm

|         | DIMENS | SIONS IN MILLI       | METERS | DIMI   | ENSIONS IN INC | CHES   |

|---------|--------|----------------------|--------|--------|----------------|--------|

| SYMBOLS | MIN    | NOM                  | MAX    | MIN    | NOM            | MAX    |

| A       | 0.80   | 0.90                 | 1.00   | 0.031  | 0.035          | 0.039  |

| A1      | 0.00   |                      | 0.05   | 0.000  |                | 0.002  |

| A2      |        | 0.2 REF              |        |        | 0.008 REF      |        |

| Е       | 3. 90  | 4.00                 | 4.10   | 0. 153 | 0. 157         | 0. 161 |

| E1      | 2. 95  | 3. 05                | 3. 15  | 0.116  | 0.120          | 0.124  |

| E2      | 1.65   | 1.75                 | 1.85   | 0.065  | 0.069          | 0.073  |

| E3      | 2. 95  | 3.05                 | 3. 15  | 0. 116 | 0.120          | 0.124  |

| D       | 3. 90  | 4.00                 | 4. 10  | 0. 153 | 0. 157         | 0. 161 |

| D1      | 0.65   | 0.75                 | 0.85   | 0.026  | 0.030          | 0.034  |

| D2      | 0.75   | 0.85                 | 0.95   | 0.029  | 0.033          | 0.037  |

| D3      | 1. 10  | 1. 20                | 1.30   | 0.043  | 0.047          | 0.051  |

| L       | 0.35   | 0.40                 | 0.45   | 0.014  | 0.016          | 0.018  |

| L1      | 0. 57  | 0.62                 | 0.67   | 0.022  | 0.024          | 0.026  |

| L2      | 0. 23  | 0.28                 | 0.33   | 0.009  | 0.011          | 0.013  |

| L3      | 0. 57  | 0.62                 | 0.67   | 0.022  | 0.024          | 0.026  |

| L4      | 0.30   | 0.35                 | 0.40   | 0.012  | 0.014          | 0.016  |

| L5      | 0.17   | 0. 27                | 0.37   | 0.007  | 0.011          | 0.015  |

| ь       | 0.20   | 0. 25                | 0.30   | 0.008  | 0.010          | 0.012  |

| e       |        | 0. 50 BSC 0. 020 BSC |        |        |                |        |

#### NOTE

- 1. CONTROLLING DIMENSION IS MILLIMETER.

- CONVERTED INCH DIMENSIONS ARE NOT NECESSARILY EXACT.

- 2. TOLERANCE: 0.05 UNLESS OTHERWISE SPECIFIED.

- 3. RADIUS ON ALL CORNER ARE 0.152 MAX., UNLESS OTHERWISE SPECIFIED.

- 4. PACKAGE WARPAGE: 0.012 MAX.

- 5. NO ANY PLASTIC FLASH ALLOWED ON THE TOP AND BOTTOM LEAD SURFACE.

- 6. PAD PLANARITY: 0.102

- 7. CRACK BETWEEN PLASTIC BODY AND LEAD IS NOT ALLOWED.

Rev 1.0 September 2018 **www.aosmd.com** Page 21 of 23

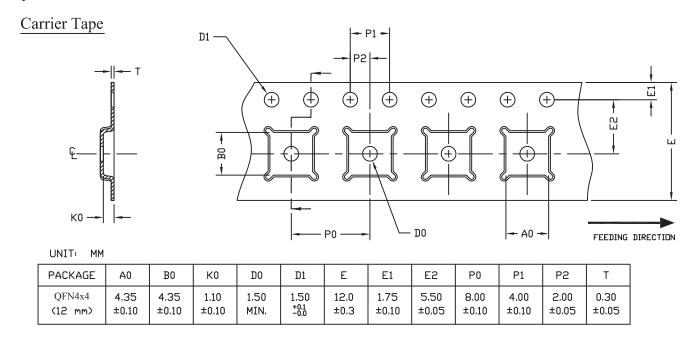

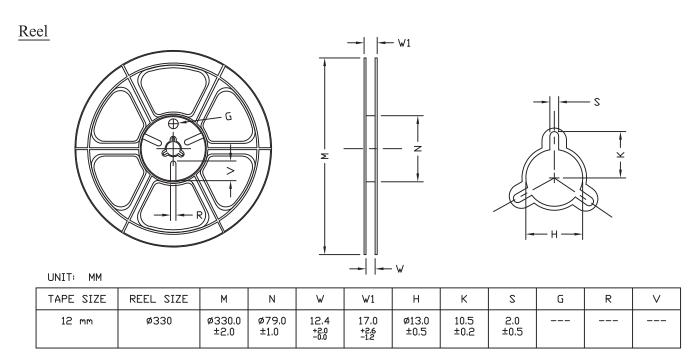

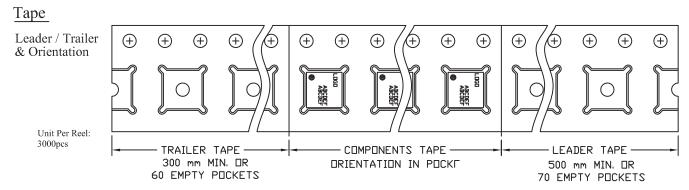

### Tape and Reel Dimensions, QFN4x4-22L, EP2\_S

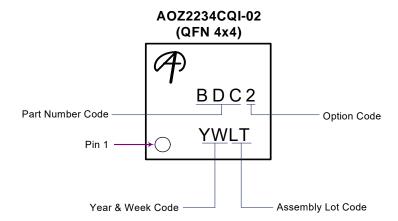

#### **Part Marking**

| Part Number   | Part Number Code of Marking |

|---------------|-----------------------------|

| AOZ2234CQI-01 | BDC1                        |

| AOZ2234CQI-02 | BDC2                        |

#### **LEGAL DISCLAIMER**

Applications or uses as critical components in life support devices or systems are not authorized. AOS does not assume any liability arising out of such applications or uses of its products. AOS reserves the right to make changes to product specifications without notice. It is the responsibility of the customer to evaluate suitability of the product for their intended application. Customer shall comply with applicable legal requirements, including all applicable export control rules, regulations and limitations.

AOS' products are provided subject to AOS' terms and conditions of sale which are set forth at: http://www.aosmd.com/terms and conditions of sale

#### LIFE SUPPORT POLICY

ALPHA AND OMEGA SEMICONDUCTOR PRODUCTS ARE NOT AUTHORIZED FOR USE AS CRITICAL COMPONENTS IN LIFE SUPPORT DEVICES OR SYSTEMS.

As used herein:

- 1. Life support devices or systems are devices or systems which, (a) are intended for surgical implant into the body or (b) support or sustain life, and (c) whose failure to perform when properly used in accordance with instructions for use provided in the labeling, can be reasonably expected to result in a significant injury of the user.

- 2. A critical component in any component of a life support, device, or system whose failure to perform can be reasonably expected to cause the failure of the life support device or system, or to affect its safety or effectiveness.

Rev 1.0 September 2018 **www.aosmd.com** Page 23 of 23