High-Current, High-Performance Smart Power Stage

### **General Description**

The AOZ52177QI is a general-purpose Smart Power Stage (SPS) consisting of two asymmetrical MOSFETs and an integrated driver for high current, high frequency DC-DC converters.

The AOZ52177QI provides an output current signal (IMON), which reports the real-time module current with a gain of 5 mV/A. The IMON signal can be directly used to replace inductor DCR sensing or resistor sensing in multiphase voltage regulator systems without the need for temperature compensation.

The AOZ52177QI also includes an accurate module temperature monitor (TMON). TMON is a voltage sourced signal with a gain of 8 mV/°C.

The MOSFETs are individually optimized for operation in the synchronous buck configuration. The High-Side MOSFET is optimized to achieve low capacitance and gate charge for fast switching with low duty cycle operation. The Low-Side MOSFET has ultra-low ON resistance to minimize conduction loss. The standard 5 mm x 6 mm QFN package is optimally designed to minimize parasitic inductance for minimal EMI signature.

### **Features**

- 3V to 25V power supply range

- 70A continuous output current

- Up to 100A for 10 ms instantaneous current

- Up to 150A for 10 μs instantaneous current

- Optimized for switching frequency up to 1.5 MHz

- Integrated current monitor (5 mV/A) with typical 5% accuracy over temperature

- Integrated temperature monitor (8 mV/°C) with 2% accuracy

- Fault Indicator

- Under-Voltage LockOut (UVLO) on VCC

- Over-Current Protection

- Zero Current Detect Function

- Over Temperature Protection

- Standard QFN5x6-39L package

### **Applications**

- Server systems

- High end CPU/GPU Power Stage

- Communications Infrastructure

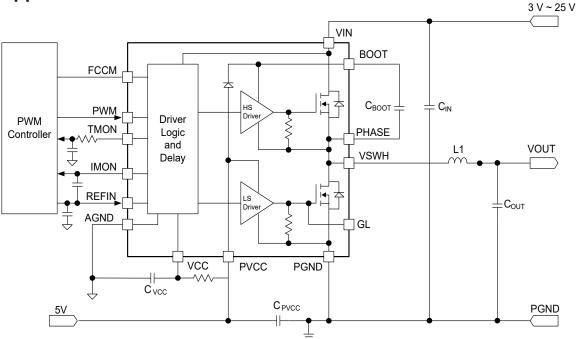

# **Typical Application**

## **Ordering Information**

| Part Number | mber Ambient Temperature Range |            | Environmental |

|-------------|--------------------------------|------------|---------------|

| AOZ52177QI  | -40°C to 125°C                 | QFN5x6-39L | RoHS          |

AOS products are offered in packages with Pb-free plating and compliant to RoHS standards. Please visit https://aosmd.com/sites/default/files/media/AOSGreenPolicy.pdf for additional information.

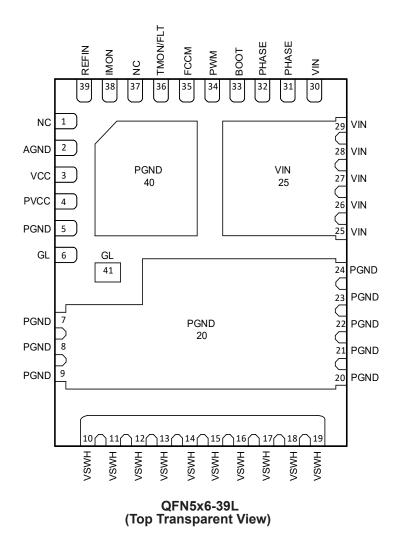

# **Pin Configuration**

# **Pin Description**

| Pin Number                                                                                                                                                                                                                                                                                                                                                                                                                                                               | Pin Name                                                                                                      | Pin Function                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | NC                                                                                                            | No connect                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| 2                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | AGND                                                                                                          | Signal Ground.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| 3                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | VCC                                                                                                           | 5V Bias for Internal Logic Blocks. Ensure to position a 1 μF MLCC directly between VCC and AGND (Pin 2).                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| 4                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | PVCC                                                                                                          | 5 V Power Rail for High-Side and Low-Side MOSFET Drivers. Ensure to position a 1 μF MLCC directly between PVCC and PGND (Pin 5).                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| 5                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | PGND                                                                                                          | Power Groundfor High-Side and Low-Side MOSFET Gate Drivers. Ensure to connect 1µF directly between PGND and PVCC (Pin4).                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| 6, 41                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | GL                                                                                                            | Low-Side MOSFET Gate connection. This is for test purposes only.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| 7, 8, 9, 20, 21, 22,<br>23, 24, 40                                                                                                                                                                                                                                                                                                                                                                                                                                       | PGND                                                                                                          | Power Ground pin for power stage (Source connection of Low-Side MOSFET).                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| 10, 11, 12, 13, 14,<br>15, 16, 17, 18, 19                                                                                                                                                                                                                                                                                                                                                                                                                                | VSWH                                                                                                          | Switching node connected to the Source of High-Side MOSFET and the Drain of Low-Side MOSFET.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| 25, 26, 27, 28,<br>29, 30                                                                                                                                                                                                                                                                                                                                                                                                                                                | VIN                                                                                                           | Power stage High Voltage Input (Drain connection of High-Side MOSFET).                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| 31, 32                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | PHASE                                                                                                         | This pin is dedicated for bootstrap capacitor AC return path connection from BOOT (Pin 33).                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| 33                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | BOOT High-Side MOSFET Gate Driver supply rail. Connect a 100 nF ceramic capacitor bet and the PHASE (Pin 32). |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| PWM input signal from Controller IC. This input is compatible with 3.3V and 5V Trilevel.                                                                                                                                                                                                                                                                                                                                                                                 |                                                                                                               | PWM input signal from Controller IC. This input is compatible with 3.3 V and 5 V Tri-State logic level.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| 35 FCCM is allowed and diode emulation mode is active when FCCM = Low. When FCCM                                                                                                                                                                                                                                                                                                                                                                                         |                                                                                                               | Continuous conduction mode of operation is triggered when FCCM = High. Discontinuous mode is allowed and diode emulation mode is active when FCCM = Low. When FCCM is tri-stated, SPS enters a low power shutdown mode                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| Temperature fault. For multi-phase application, the TMON/FLT pin can be connected toge common bus. The highest voltage representing the highest temperature among all phase sent to the PWM controller. No more than 470 pF total capacitance can be directly connected TMON/FLT and AGND (Pin 2). A higher capacitance load is allowed with a series resistor (up to 1 nF. At 0°C and in normal operation, the output voltage is 0.6V with a temperature connected toge |                                                                                                               | Temperature Monitor and Fault Flag Pin. TMON/FLT will be pulled HI (~3.3 V) to indicate an Over-Temperature fault. For multi-phase application, the TMON/FLT pin can be connected together as a common bus. The highest voltage representing the highest temperature among all phases will be sent to the PWM controller. No more than 470 pF total capacitance can be directly connected across TMON/FLT and AGND (Pin 2). A higher capacitance load is allowed with a series resistor (~1 k $\Omega$ ) for up to 1 nF. At 0°C and in normal operation, the output voltage is 0.6V with a temperature coefficient value of 8 mV/°C. There is an internal pull up source to 3.3 V when a fault condition occurs. |

| 37                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | NC                                                                                                            | No connect                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| 38                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | IMON                                                                                                          | Current Monitor output signal referenced to REFIN (Pin 39). Connect the IMON output to the appropriate Current Sense input of the controller. No more than 47 pF capacitance can be directly connected across IMON and REFIN pins. With a $100\Omega$ series resistor, up to 470 pF may be used.                                                                                                                                                                                                                                                                                                                                                                                                                 |

| 39                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | REFIN                                                                                                         | Input for external reference voltage for IMON (Pin 38). This voltage should be between 0.7 V and 2.0 V. Nominal value is 1.2 V. Place a low ESR ceramic capacitor (~ 0.1 µF) from this pin to AGND (Pin 2). Connect REFIN to the appropriate Current Sense Reference output from the controller.                                                                                                                                                                                                                                                                                                                                                                                                                 |

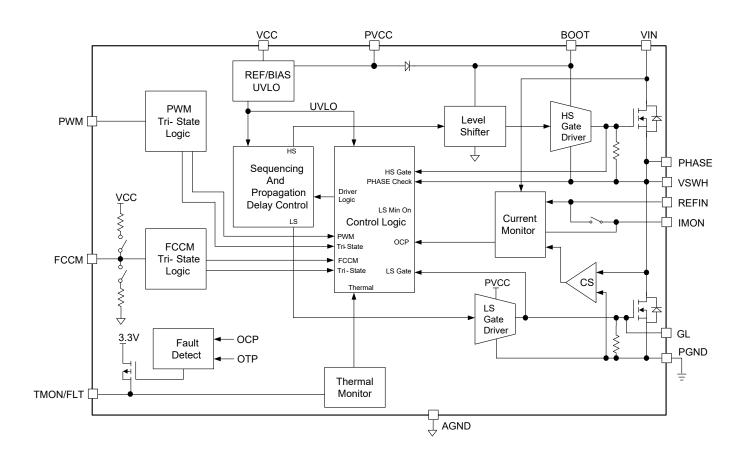

# **Functional Block Diagram**

## **Absolute Maximum Ratings**

Exceeding the Absolute Maximum ratings may damage the device.

| Parameter                                       | Rating                            |

|-------------------------------------------------|-----------------------------------|

| Low Voltage Supply (VCC, PVCC)                  | -0.3 V to 6 V                     |

| High Voltage Supply (VIN)                       | -0.3 V to 30 V                    |

| Control Inputs (PWM, FCCM)                      | -0.3 V to<br>(VCC + 0.3 V)        |

| Output (TMON/FLT, IMON)                         | -0.3 V to<br>(VCC + 0.3 V)        |

| Bootstrap Voltage DC (BOOT-PGND)                | -0.3 V to 35 V                    |

| Bootstrap Voltage Transient (1) (BOOT-PGND)     | -8V to 40V                        |

| Bootstrap Voltage DC<br>(BOOT-PHASE/VSWH)       | -0.3 V to 6 V                     |

| BOOT Voltage Transient (1)<br>(BOOT-PHASE/VSWH) | -0.3V to 9V                       |

| Switch Node Voltage DC (PHASE/VSWH)             | -0.3 V to 30 V                    |

| Switch Node Voltage Transient (1) (PHASE/VSWH)  | -8V to 38V                        |

| Low-Side Gate Voltage DC (GL)                   | (PGND - 0.3V) to<br>(PVCC + 0.3V) |

| Low-Side Gate Voltage Transient (1) (GL)        | (PGND - 2.5V) to<br>(PVCC + 0.3V) |

| VSWH Current DC                                 | 70A                               |

| VSWH Current 10ms Pulse                         | 100A                              |

| VSWH Current 10us Pulse                         | 150A                              |

| Storage Temperature (TS)                        | -65°C to +150°C                   |

| Max Junction Temperature (TJ)                   | 150°C                             |

| ESD Rating (2)                                  | ±2 kV HBM<br>±1 kV CDM            |

#### Notes:

- 1. Peak voltages can be applied for  $10\,\mathrm{ns}$  per switching cycle.

- 2. Devices are inherently ESD sensitive, handling precautions are required. Human body model rating:  $1.5\,\Omega$  in series with 100 pF.

## **Recommended Operating Conditions**

The device is not guaranteed to operate beyond the Maximum Recommended Operating Conditions.

| Parameter                                     | Rating             |

|-----------------------------------------------|--------------------|

| High Voltage Supply (VIN)                     | 3 V to 25 V        |

| Low Voltage/ MOSFET Driver Supply (VCC, PVCC) | 4.5V to 5.5V       |

| Control Inputs<br>(PWM, FCCM)                 | 0 V to VCC         |

| Output (TMON/FLT, IMON)                       | 0 V to VCC         |

| Operating Frequency                           | 200 kHz to 1.5 MHz |

## Electrical Characteristics(3)

$T_J$  = 25°C to 125°C. Typical values reflect 25°C ambient temperature; VIN = 12V, VCC = PVCC = 5V, unless otherwise specified.

| Symbol                          | Parameter                              | Conditions                              | Min  | Тур | Max  | Unit |

|---------------------------------|----------------------------------------|-----------------------------------------|------|-----|------|------|

| General                         |                                        |                                         |      |     |      |      |

| $V_{VIN}$                       | Power Stage Power Supply               |                                         | 3    |     | 25   | V    |

| V <sub>CC</sub>                 | Low Voltage Bias Supply                | PVCC = VCC                              | 4.5  |     | 5.5  | V    |

| R <sub>0JC</sub> <sup>(4)</sup> |                                        | PCB Temp = 100°C                        |      | 1.5 |      | °C/W |

| R <sub>θJA</sub> <sup>(4)</sup> | Thermal Resistance                     | Fsw = 600 kHz, Vo = 1 V. AOS Demo Board |      | 12  |      | °C/W |

| Input Supply                    | and UVLO                               |                                         |      |     | ı    |      |

| V <sub>CC_UVLO</sub>            |                                        | VCC Rising                              | 3.4  | 3.8 | 4.2  | V    |

| V <sub>CC_HYST</sub>            | VCC Under-Voltage Lockout              | VCC Hysteresis                          |      | 400 |      | mV   |

| t <sub>VCC_DEL</sub>            | VCC Power On Delay                     | From VCC UVLO release                   |      | 100 |      | μs   |

|                                 |                                        | FCCM = H or L                           |      | 4   |      | mA   |

| l <sub>vcc</sub>                | Control Circuit Bias Current           | FCCM = Floating                         |      | 4   |      | mA   |

|                                 |                                        | FCCM = Floating                         |      |     | 1    | μA   |

| I <sub>PVCC</sub>               | Drive Circuit Operating Current        | PWM = 300 kHz, 20% Duty Cycle           |      | 13  |      | mA   |

|                                 |                                        | PWM = 600 kHz, 20% Duty Cycle           |      | 26  |      | mA   |

| PWM Input                       |                                        |                                         |      |     |      |      |

| $V_{PWMH}$                      | PWM Logic High Input Voltage           |                                         |      |     | 2.85 | V    |

| V <sub>PWML</sub>               | PWM Logic Low Input Voltage            |                                         | 0.65 |     |      | V    |

| R <sub>PWM_DOWN</sub>           | DIAMA Dia lagasit Compart              | Pull down                               |      | 16  |      | kΩ   |

| $R_{PWM\_UP}$                   | PWM Pin Input Current                  | Pull up                                 |      | 33  |      | kΩ   |

| V <sub>PWM_TRI</sub>            | PWM Tri-State Window                   |                                         | 1.1  |     | 2.1  | V    |

| V <sub>PWM_FLOAT</sub>          | PWM Tri-State Voltage Clamp            | PWM = Floating                          | 1.5  | 1.7 | 1.9  | V    |

| t <sub>PWM_SKIP</sub>           | Minimum PWM Pulse Detection            |                                         |      |     | 10   | ns   |

| t <sub>PWMH_MIN</sub>           | Forced Minimum High-side On Pulse      |                                         |      | 20  |      | ns   |

| t <sub>PWML_MIN</sub>           | Forced Minimum Low-side on Pulse       |                                         |      | 60  |      | ns   |

| FCCM Input                      |                                        |                                         |      |     |      |      |

| V <sub>FCCMH</sub>              | FCCM Logic High Input Voltage          |                                         |      |     | 2.85 | V    |

| V <sub>FCCML</sub>              | FCCM Logic Low Input Voltage           |                                         | 0.65 |     |      | V    |

| R <sub>FCCM_DOWN</sub>          | 50011 (5.1)                            | Pull down                               |      | 100 |      | kΩ   |

| R <sub>FCCM_UP</sub>            | FCCM Input Resistance                  | Pull up                                 |      | 200 |      | kΩ   |

| V <sub>FCCM_TRI</sub>           | FCCM Tri-State Window                  |                                         | 1.1  |     | 2.1  | V    |

| V <sub>FCCM_FLOAT</sub>         | FCCM Tri-State Voltage Clamp           | FCCM = Floating                         | 1.5  | 1.7 | 1.9  | V    |

| t <sub>PD_EN</sub>              | Propagation Delay for PWM<br>Operation | FCCM from Tri-State to H or L           |      | 4   |      | μs   |

| t <sub>PD_DIS</sub>             | Propagation Delay for Disable          | FCCM from H or L to Tri-State           |      | 5   |      | μs   |

## Electrical Characteristics(3)

$T_J$  = 25°C to 125°C. Typical values reflect 25°C ambient temperature; VIN = 12V, VCC = PVCC = 5V, unless otherwise specified.

| Symbol                 | Parameter                           | Conditions                                                                                                                                | Min   | Тур  | Max   | Unit     |

|------------------------|-------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------|-------|------|-------|----------|

| Zero Cross D           | etect (ZCD) Function                |                                                                                                                                           |       |      |       |          |

| I <sub>ZCD_OFS</sub>   | ZCD Current Threshold Offset        | PWM = L, Inductor = 150 nH,<br>VOUT = 0.6 V, F <sub>SW</sub> = 600 kHz                                                                    |       | 2    |       | Α        |

| t <sub>ZCD_BLK</sub>   | ZCD Blanking Time                   | PWM = L                                                                                                                                   |       | 250  |       | ns       |

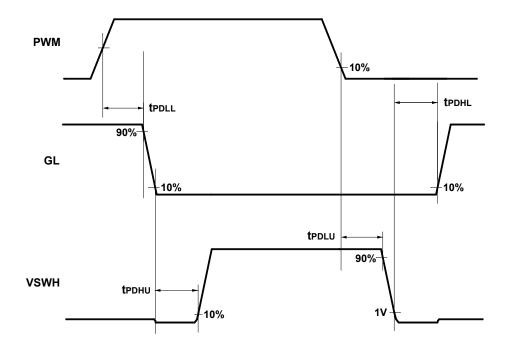

| Gate Driver T          | iming                               |                                                                                                                                           |       |      |       |          |

| t <sub>PDLU</sub>      | PWM to High-Side Gate               | PWM: $H \rightarrow L$ , VSWH: $H \rightarrow L$                                                                                          |       | 25   |       |          |

| t <sub>PDLL</sub>      | PWM to Low-Side Gate                | PWM: $L \rightarrow H$ , GL: $H \rightarrow L$                                                                                            |       | 20   |       |          |

| t <sub>PDHU</sub>      | Low-side to High-Side Gate Deadtime | GL: $H \rightarrow L$ , $GH^{(5)}$ : $L \rightarrow H$                                                                                    |       | 15   |       |          |

| t <sub>PDHL</sub>      | High-Side to Low-side Gate Deadtime | VSWH: $H \rightarrow 1V$ , GL: $L \rightarrow H$                                                                                          |       | 8    |       | ns       |

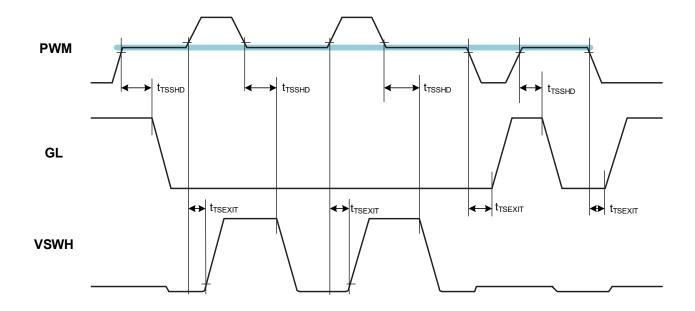

| t <sub>TSSHD</sub>     | Tri-State Shutdown Delay            | PWM: L $\rightarrow$ V <sub>PMW_TRI</sub> , GL: H $\rightarrow$ L and PWM: H $\rightarrow$ V <sub>PMW_TRI</sub> , VSWH: H $\rightarrow$ L | 15    |      | 50    |          |

| t <sub>TSEXIT</sub>    | Tri-State Propagation Delay         | PWM: $V_{PMW\_TRI}$ , $\rightarrow$ H, VSWH: $L \rightarrow$ H<br>PWM: $V_{PMW\_TRI}$ , $\rightarrow$ L, GL: $L \rightarrow$ H            |       |      | 30    |          |

| IMON Timing            | and Operating Range, and Accurac    | cy                                                                                                                                        |       |      |       |          |

| t <sub>FALL_BLK</sub>  | VSWH Falling Blanking Time          |                                                                                                                                           |       | 250  |       | ns       |

| t <sub>PRO_DEL</sub>   | IL to IMON Propagation Delay        | L = 150 nH, FSW = 600 kHz, VOUT = 1.8 V<br>IMON Valley to IL Valley                                                                       |       | 60   | 75    | ns       |

| V <sub>REFIN</sub>     | REFIN Voltage Range                 |                                                                                                                                           | 0.7   | 1.2  | 2.0   | <b>V</b> |

| V <sub>IMON</sub>      | IMON Voltage Range                  |                                                                                                                                           | 0.3   |      | 3     | V        |

| C <sub>IMON</sub>      | Max IMON Output Capacitance         | Across IMON and REFIN                                                                                                                     | 10    |      | 47    | pF       |

|                        | Allowed                             | With $100 \Omega$ resistor in series                                                                                                      |       |      | 470   | pF       |

| A <sub>IMON</sub>      | IMON Gain                           | CCM                                                                                                                                       |       | 5    |       | mV/A     |

| $V_{IMON\_ACC}$        | IMON Accuracy                       | -10A < IOUT < 10A                                                                                                                         | -1    |      | 1     | Α        |

|                        | •                                   | 10A < IOUT < 80A                                                                                                                          |       | +/-3 |       | %        |

| V <sub>IMON_OFF</sub>  | Current-sense offset                | VCS = 1.2 V, TJ = 25°C                                                                                                                    | -2    |      | +2    | mV       |

| TMON Operat            | ing Range and Over-Temperature      |                                                                                                                                           |       | I    | I     |          |

| A <sub>TMON_SLP</sub>  | TMON Slope Gain                     | No Load                                                                                                                                   | 7.8   | 8    | 8.2   | mV/°C    |

| V <sub>TMON_25C</sub>  | TMON Voltage at 25°C                | $V(T_{JCT}) = 0.6V + (8mV \times T_{JCT})$                                                                                                | 0.784 | 0.8  | 0.816 | V        |

| V <sub>TMON_125C</sub> | TMON Voltage at 125°C               | $V(T_{JCT}) = 0.6V + (8mV \times T_{JCT})$                                                                                                | 1.56  | 1.6  | 1.64  | V        |

| I <sub>TMON_SOUR</sub> | TMON Sourcing Current               | TMON = 0 V                                                                                                                                |       | 400  |       | μΑ       |

| I <sub>TMON_SINK</sub> | TMON Sinking Current                | TMON = 3.3 V                                                                                                                              |       | 25   |       | μA       |

| T <sub>OTP</sub>       | Over-Temperature Threshold          | Temperature Rising                                                                                                                        | 135   | 145  | 155   | °C       |

| T <sub>OTP_HYST</sub>  | Over-Temperature Hysteresis         |                                                                                                                                           |       | 20   |       | °C       |

## Electrical Characteristics(3)

$T_J$  = 25°C to 125°C. Typical values reflect 25°C ambient temperature; VIN = 12 V, VCC = PVCC = 5 V, unless otherwise specified.

| Symbol                 | Parameter                                           | Conditions       | Min | Тур | Max | Unit   |  |

|------------------------|-----------------------------------------------------|------------------|-----|-----|-----|--------|--|

| Current Limit          |                                                     |                  |     |     |     |        |  |

| I <sub>LIM</sub>       | Over Current Limit                                  |                  |     | 120 |     | Α      |  |

| I <sub>LIM_HYS</sub>   | Over Current Limit Hysteresis                       |                  |     | 15  |     | Α      |  |

| N <sub>OC_COUNT</sub>  | OC Counts before Reporting Fault and HS Latches Off |                  |     | 10  |     | Counts |  |

| Fault Output Indicator |                                                     |                  |     |     |     |        |  |

| I <sub>TMON_FLT</sub>  | TMON/FLT Output Current at Fault Conditions         | TMON/FLT = 2.5 V | 4   |     |     | mA     |  |

| t <sub>TMON_FLT</sub>  | TMON/FLT Fault Report Delay                         |                  |     | 22  |     | ns     |  |

#### Notes:

- 3. All voltages are specified with respect to the corresponding AGND pin.

- 4. Characterization value. Not tested in production.

- 5. GH is an internal pin.

# **Timing Diagrams**

**Figure 1. PWM Logic Input Timing Diagram**

Figure 2. PWM Tri-State Hold Off and Exit Timing Diagram

Rev. 1.2 August 2024 **www.aosmd.com** Page 9 of 15

### **Application Information**

AOZ52177QI is a fully integrated smart power module designed to work over an input voltage range of 3V to 25V with 5V supplies for gate drive and internal control circuits. This smart power stage module features accurate current monitoring (IMON) which provides both High-Side and Low-Side MOSFET current information in both constant current and diode emulated mode operation. It also features temperature monitoring (TMON) which provides continuous thermal reading of the module temperature. Additional features such as Control Circuit Input Voltage (VCC) UVLO and light load efficiency control.

The High-Side and Low-Side MOSFETs are combined into one package with the pin configuration optimized for power routing with minimum parasitic inductance. The MOSFETs are individually tailored for efficient operation in low duty cycle synchronous buck converter applications. In addition, a high current driver is also included in the package to minimize the gate drive loop delay resulting in extremely fast switching

### **Powering the Module and the Gate Drives**

An external 5V supply (PVCC) is required for driving the MOSFETs. The MOSFETs are designed with low gate thresholds so that lower drive voltage can be used to reduce the switching and drive losses without compromising the conduction losses. The integrated gate driver is capable of supplying high peak current into the gate of Low-Side MOSFET to achieve extremely fast switching. A ceramic bypass capacitor of  $1\,\mu\text{F}$  or higher is recommended from PVCC to PGND. For effective filtering it is strongly recommended to have a direct connection from this capacitor to PGND.

The boost supply for driving the High-Side MOSFET is generated by connecting a small capacitor between BOOT pin and the switching node (PHASE). It is recommended that this capacitor *Cboot* should be connected as close as possible to the device across PHASE (Pin 19) and BOOT (Pin 20). Rboot is an optional external resistor that can be used by designers to slow down the turn on speed of the High-Side MOSFET. Selecting the *Rboot* value is a compromise between switching speed and the amplitude of power switching node (VSWH) voltage spikes. Typical values of *Rboot* are between  $1\,\Omega$  and  $5\,\Omega$ .

#### Power-On Reset (POR)

During initial start-up, VCC voltage rise is monitored. Once the rising VCC voltage exceeds 3.4 V ( $V_{VCC\_UVLO}$ ) and FCCM is High or Low, normal operation of the driver is enabled. The PVCC voltage is not being monitored as it should be connected to VCC. VCC POR is gated to the TMON/FLT pin, which resumes normal TMON operation 8  $\mu$ s after VCC is above their POR levels and no other faults occur.

The AOZ52177QI must be powered up before the PWM input is applied. During start-up it is necessary for the PWM signal to go through a proper soft start sequence to minimize inrush current in the converter. Powering the module with a full duty cycle PWM signal applied may lead to a number of undesirable consequences.

#### **FCCM Input**

FCCM is a Tri-State compatible input. When FCCM = Low, Discontinuous Conduction Mode (DCM) is allowed, and diode emulation is active when with the built-in Zero Cross Detection (ZCD) features. When FCCM = High, AOZ52177QI enters Continuous Conduction Mode (CCM) mode, where VSWH follows the state of PWM. When FCCM = Floating, the driver shuts down to a low power state.

The FCCM Threshold in Table 1 lists the thresholds for high-level and low-level logic, as well as Tri-State operation.

Table 1. FCCM Input and Tri-State Thresholds

| Parameters | V <sub>FCCMH</sub> | V <sub>FCCML</sub> | V <sub>TRI(L)</sub> | V <sub>TRI(H)</sub> |

|------------|--------------------|--------------------|---------------------|---------------------|

| Thresholds | 2.85 V             | 0.65 V             | 1.1 V               | 2.1 V               |

### **PWM Input**

The AOZ52177QI is compatible with 3.3 V and 5 V PWM input logic and supports Tri-State PWM. When the input is high impedance or left open, both the gate drive outputs will be turned off and the Low-Side and High-Side gates are actively held low. The PWM Threshold in Table 2 lists the thresholds for high-level and low-level logic, as well as Tri-State operation.

Table 2. PWM Input and Tri-State Thresholds

| Parameters | V <sub>PWMH</sub> | V <sub>PWMH</sub> | V <sub>TRI(L)</sub> | V <sub>TRI(H)</sub> |

|------------|-------------------|-------------------|---------------------|---------------------|

| Thresholds | 2.85 V            | 0.65 V            | 1.1 V               | 2.1 V               |

The AOZ52177QI is compatible with standard multiphase controllers as well as other controller IC's utilizing 5 V and 3.3 V PWM logic. If the PWM input is being pulled into and remains in the Tri-State window for a set hold-off time ( $t_{TSEXIT}$ ), the driver will force both MOSFETs to their off state. When the PWM signal moves outside the Tri-State window, the driver immediately resumes operation and drives the MOSFETs according to the PWM input.

This feature allows the controller to use PWM as a method of forcing both MOSFETs to be off. For the condition that the PWM input is floating, the pin will be pulled into the Tri-State Clamp Voltage ( $V_{PWM\_FLOAT}$ ) internally, thus forcing both MOSFETs to a safe off state. Table 3 shows the logic truth table for PWM and FCCM inputs.

Table 3. GH and GL Operation Truth Table

| FCCM      | PWM       | <b>GH</b> <sup>(6)</sup> | GL |

|-----------|-----------|--------------------------|----|

| Tri-State | X         | 0                        | 0  |

| 0         | 1         | 1                        | 0  |

| 0         | 0         | 0                        | 1  |

| 1         | 1         | 1                        | 0  |

| 1         | 0         | 0                        | 1  |

| X         | Tri-State | 0                        | 0  |

#### Note:

6. GH signal is not available on package level

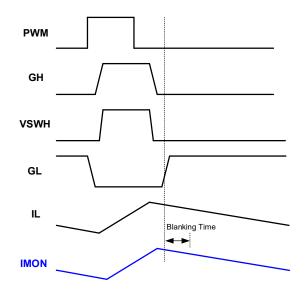

### **Current Monitoring (IMON)**

An accurate Current Sense Amplifier monitors the current through the Low-Side MOSFET. A voltage signal proportional to that current appears at the IMON (Pin 25), relative to REFIN (Pin 24), at a current sense gain of 5 mV/A. Both IMON and REFIN should be connected to the appropriate current sense inputs of the controller. This IMON signal effectively eliminates the needs of using external sense resistor or inductor DCR sensing.

Figure 3 shows the Low-Side MOSFET current sense mechanism. After the falling edge of the PWM, there are two delays:

- The expected propagation delay from PWM to VSWH (t<sub>PDLU</sub>)

- 2. The blanking delay to allow time for the transition to settle  $(t_{\text{FALL BLK}})$

The IMON signal approximates the actual inductor current waveform.

Figure 3. Commutating Current Re-Construction at IMON

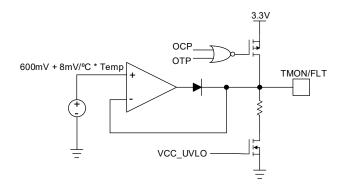

#### Temperature Monitoring (TMON/FLT)

AOZ52177QI monitors its internal temperature and provides a signal proportional to that temperature on the TMON/FLT pin. TMON/FLT has a voltage of 600 mV at 0 °C and temperature gain of 8 mV/°C (A<sub>TMON\_SLP</sub>). Figure 4 shows a simplified functional representation. The top section represents the protection fault that will pull the output high. The mid-section shows the symbolic sensor and the output buffer. The bottom section will set the initial state of TMON/FLT before the module is active. The TMON/FLT pin is configured internally such that a user can tie multiple pins together externally and the resulting TMON/FLT bus will assume the voltage of the highest contributor (representing the highest temperature).

Figure 4. Temperature Monitor Internal Circuit

#### **Zero Cross Detect (ZCD)**

ZCD will detect the valley current when Low-Side MOSFET is on. If the current is less than 2A ( $I_{ZCD\_OFS}$ ), the Low-Side MOSFET will be turned off independent of PWM logic level. This is an automatic light load mechanism and suitable for most analog PWM controllers.

#### **Over Temperature Protection (OTP)**

If the internal temperature exceeds the Over-Temperature threshold ( $T_{OTP}$ ), the TMON/FLT (Pin 36) is pulled to 3.3V after 100 ns ( $t_{TMON/FLT}$ ) delay. Both High-Side and Low-Side MOSFETs are turned off under OTP condition. The TMON/FLT will remain in the fault mode until the junction temperature drops below the hysteresis threshold ( $T_{OTP\_HYST}$ ). At that point, the TMON/FLT and IMON pins resume normal operation.

### **Over Current Protection (OCP)**

An Over Current Protection (OCP) fault is detected when the current running through the power stage exceeds 120 A ( $I_{LIM}$ ). When the OCP is detected, the High-Side MOSFET ON time will be truncated to a maximum of 400 ns for

Rev. 1.2 August 2024 www.aosmd.com Page 11 of 15

every switching cycle. If the OCP event is trigged 10 times ( $N_{\text{OC\_COUNT}}$ ) consecutively, TMON/FLT (Pin 1) will be internally pulled to 3.3V to indicate a fault condition.

The FAULT flag will be released by a power reset or the output current is 15 A less than the OCP threshold.

#### **FAULT Reporting**

These 4 protection functions will trigger the fault reporting at TMON/FLT (Pin 1):

- 1. VCC Under-Voltage Lock-Out (UVLO)

- 2. Over-Current Protection (OCP)

- 3. Over-Temperature Protection (OTP)

For UVLO function, TMON/FLT will be pulled down to ground to indicate under voltage fault condition.

For OCP and OTP reporting, TMON/FLT will be pulled high to 3.3V to indicate the fault condition. At the same time, both High-Side and Low-Side MOSFETs will be turned off to protect the module from over-heating. The PWM controller should quickly recognize when it is outside normal operating conditions.

All of the above faults are summarized in Table 4.

Table 4. GH and GL Operation Truth Table

| Fault       | Respose                                                                                               |

|-------------|-------------------------------------------------------------------------------------------------------|

| VCC<br>UVLO | Fault Flag pulled down only                                                                           |

| OCP         | Fault Flag pulled to 3.3 V after 10 consecutive occurrences High-Side MOSFET maximum on time = 400 ns |

| OTP         | Fault Flag pulled to 3.3 V<br>Both MOSFETs are off                                                    |

### **Protection Feature and Function Summary**

**Table 5. Protection Feature and Function Summary**

| Protection                                        | Entry Condition                                                                                                                                            | Action                                                                           | Release Condition                                                                                                      |

|---------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------|

| Over Current Protection (OCP) See Protection Case | •10 consecutive occurrences of |                                                                                  | Power reset (UVLO_VCC) or consecutive cycles of load current below OCP falling threshhold or PMW to tri-state for 2 µs |

| Zero Current<br>Detection (ZCD)                   | <ul> <li>IMON valley sensing</li> <li>Inductor current &lt; 2A as reported by IMON</li> <li>Blanking time of (LS on state) is 250 ns</li> </ul>            | •LS off until next cycle                                                         | • PWM rising                                                                                                           |

| Over Temparature<br>Protection (OTP)              | •TMON sensing •TMON voltage above 1.69 V (136°C)                                                                                                           | •Turn off both HS and LS •TMON/FLT pull up to 3.3 V                              | •TMON voltage below 1.57V<br>(121°C)                                                                                   |

| Driver IC Supply UVLO (VCC_UVLO)                  | <ul><li>VCC sensing</li><li>VCC voltage below 3.4 V</li><li>No PVCC sensing</li></ul>                                                                      | HS, LS, TMON & IMON are disabled     TMON/FLT pull low     IMON Shorted to REFIN | VCC voltage above 3.8 V     (400 mV Hysteresis)                                                                        |

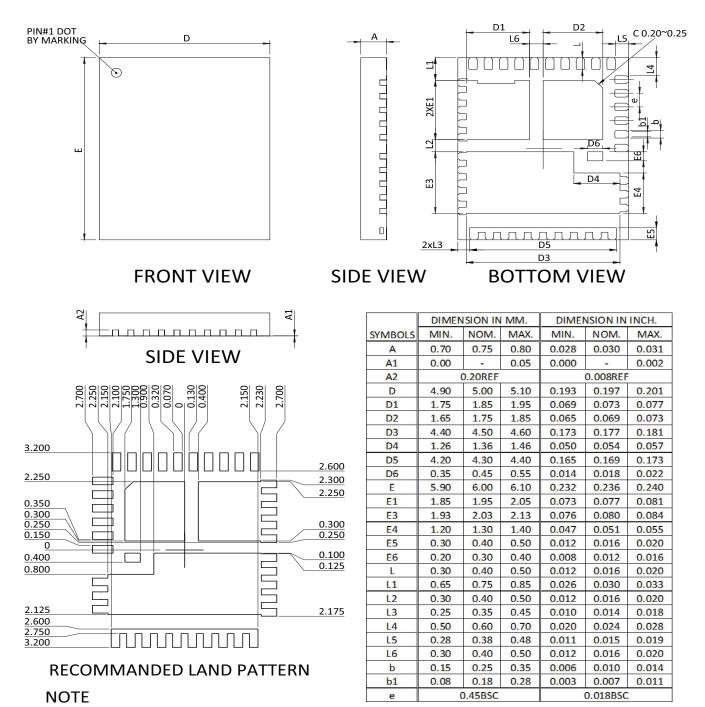

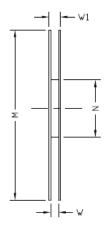

## Package Dimensions, QFN5x6-39L

- 1.CONTROLLING DIMENSION IS MILLIMETER.

- 2.CONVERTED INCH DIMENSIONS ARE NOT NECESSARILY EXACT.

Rev. 1.2 August 2024 **www.aosmd.com** Page 13 of 15

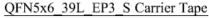

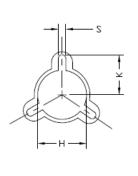

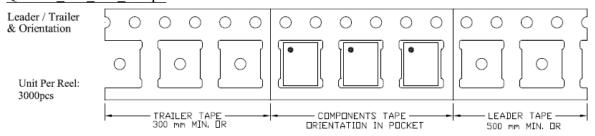

# Tape and Reel Dimensions, QFN5x6-39L

UNIT: MM

| PACKAGE | A0            | В0            | K0            | DO                      | D1                      | V                       | Ε             | F             | P0            | P1            | P2            | Т             |

|---------|---------------|---------------|---------------|-------------------------|-------------------------|-------------------------|---------------|---------------|---------------|---------------|---------------|---------------|

| QFN5X6  | 5.30<br>±0.10 | 6.30<br>±0.10 | 1.15<br>±0.10 | Ø1,50<br>+0,10<br>-0,00 | Ø1.50<br>+0.20<br>-0.00 | 12.00<br>+0.30<br>-0.10 | 1,75<br>±0.10 | 5.50<br>±0.05 | 4.00<br>±0.10 | 8,00<br>±0.10 | 2.00<br>±0.05 | 0.30<br>±0.03 |

UNIT: MM

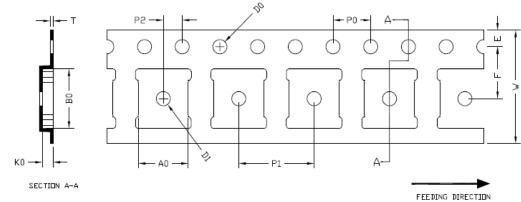

| TAPE SIZE | REEL SIZE | М             | N               | W             | W1             | Н                     | К    | 2             | G | R | V |

|-----------|-----------|---------------|-----------------|---------------|----------------|-----------------------|------|---------------|---|---|---|

| 12 mm     | Ø330      | ø330<br>±0.50 | ø97.00<br>±0.10 | 13.0<br>±0.30 | 17.40<br>±1.00 | Ø13.0<br>+0.5<br>-0.2 | 10.6 | 2.00<br>±0.50 |   |   |   |

### QFN5x6\_39L\_EP3\_S Tape

Rev. 1.2 August 2024 **www.aosmd.com** Page 14 of 15

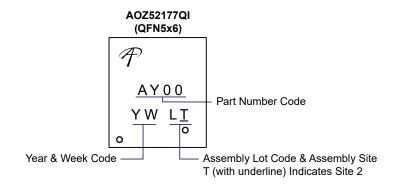

### **Part Marking**

#### LEGAL DISCLAIMER

Applications or uses as critical components in life support devices or systems are not authorized. Alpha and Omega Semiconductor does not assume any liability arising out of such applications or uses of its products. AOS reserves the right to make changes to product specifications without notice. It is the responsibility of the customer to evaluate suitability of the product for their intended application. Customer shall comply with applicable legal requirements, including all applicable export control rules, regulations and limitations.

AOS's products are provided subject to AOS's terms and conditions of sale which are set forth at: http://www.aosmd.com/terms\_and\_conditions\_of\_sale

#### LIFE SUPPORT POLICY

ALPHA AND OMEGA SEMICONDUCTOR PRODUCTS ARE NOT AUTHORIZED FOR USE AS CRITICAL COMPONENTS IN LIFE SUPPORT DEVICES OR SYSTEMS.

As used herein:

1. Life support devices or systems are devices or systems which, (a) are intended for surgical implant into the body or when properly used in accordance with instructions for use provided in the labeling, can be reasonably expected to result in a significant injury of the user.

2. A critical component in any component of a life support, device, or system whose failure to perform can be (b) support or sustain life, and (c) whose failure to perform reasonably expected to cause the failure of the life support device or system, or to affect its safety or effectiveness.

Page 15 of 15 Rev. 1.2 August 2024 www.aosmd.com